# UNISONIC TECHNOLOGIES CO., LTD

### LV2622

#### LINEAR INTEGRATED CIRCUIT

## 250μA, 3MHZ, LOW VOLTAGE **RAIL-TO-RAIL I/O CMOS DUAL OP AMPS**

#### **DESCRIPTION**

The UTC LV2622 is low noise, low voltage and low power dual operational amplifiers that can be designed into a wide range of applications. With a 3MHz unity-gain frequency and a guaranteed 1.7V/µs slew rate, the quiescent current is only 250µA/amplifier (5.0V).

The UTC LV2622 provides rail-to-rail output swing into heavy loads. The input common-mode voltage range includes ground and the maximum input offset voltage is 3mV. It is specified over the extended industrial temperature range (-40°C~+125°C). The operating range is 2.5V~5.5V. The UTC LV2622 provides optimal performance in low voltage and low noise systems.

#### **FEATURES**

- \* Low Cost

- \* Rail-to-Rail Output Swing

- \* Input Rail: 0.1V~+5.6V with V<sub>S</sub>=5.5V

- \* Typical Vos: 0.7mV

- \* Gain-Bandwidth Product: 3MHz

- \* High Slew Rate: 1.7V/µs

- \* Settling Time to 0.1% with 2V Step: 2.1µs

- \* Overload Recovery Time: 1µs \* Low Noise Voltage: 12nV/ √Hz

- \* Operates on 2.5V~5.5V Supplies

- \* Low Power: 250µA/Amplifier Typical Supply Current

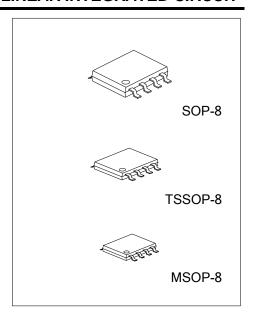

#### **ORDERING INFORMATION**

| Ordering Number |               | Daakaga | Dooking   |  |

|-----------------|---------------|---------|-----------|--|

| Lead Free       | Halogen Free  | Package | Packing   |  |

| LV2622L-P08-R   | LV2622G-P08-R | TSSOP-8 | Tape Reel |  |

| LV2622L-S08-R   | LV2622G-S08-R | SOP-8   | Tape Reel |  |

| LV2622L-SM1-R   | LV2622G-SM1-R | MSOP-8  | Tape Reel |  |

www.unisonic.com.tw 1 of 8

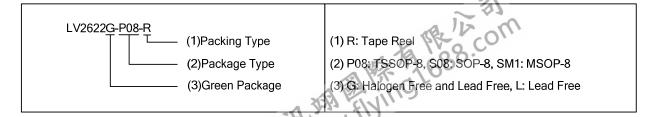

#### **MARKING**

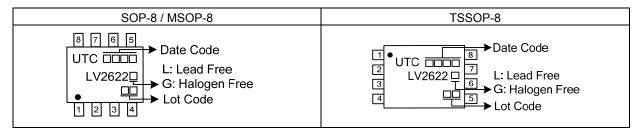

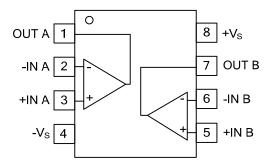

#### **PIN CONFIGURATION**

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATING** (T<sub>A</sub>=+25°C, unless otherwise specified)

| PARAMETER                 | SYMBOL           | RATINGS               | UNIT |

|---------------------------|------------------|-----------------------|------|

| Supply Voltage, V+ ~ V-   | Vs               | 7.5                   | V    |

| Common-Mode Input Voltage | $V_{CM}$         | (-Vs)-0.5 ~ (+Vs)+0.5 | V    |

| Junction Temperature      | $T_J$            | +150                  | °C   |

| Operating Temperature     | $T_OPR$          | -40 ~ +125            | °C   |

| Storage Temperature       | T <sub>STG</sub> | -65 ~ <b>+</b> 150    | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

#### THERMAL DATA

| PARAMETER                                  |         | SYMBOL          | RATINGS | UNIT |

|--------------------------------------------|---------|-----------------|---------|------|

| Junction to Ambient @ T <sub>A</sub> =25°C | TSSOP-8 |                 | 190     | °C/W |

|                                            | SOP-8   | θ <sub>JA</sub> | 125     | °C/W |

|                                            | MSOP-8  |                 | 216     | °C/W |

#### **ELECTRICAL CHARACTERISTICS**(T<sub>A</sub>=+25°C,V<sub>S</sub>=5V,V<sub>CM</sub>=V<sub>S</sub>/2,R<sub>L</sub>=600Ω, unless otherwise specified)

| PARAMETER                         | SYMBOL                   | TEST CONDITIONS                                 |              | MIN        | TYP                                              | MAX   | UNIT         |  |

|-----------------------------------|--------------------------|-------------------------------------------------|--------------|------------|--------------------------------------------------|-------|--------------|--|

| INPUT CHARACTERISTICS             |                          |                                                 |              |            |                                                  |       |              |  |

| Input Offset Voltage              | V <sub>OS</sub>          |                                                 |              |            | 0.7                                              | 3     | mV           |  |

|                                   |                          | (Note)                                          |              |            |                                                  | 3.5   |              |  |

| Input Bias Current                | $I_{B}$                  |                                                 |              |            | 1                                                |       | pА           |  |

| Input Offset Current              | los                      |                                                 |              |            | 1                                                |       | pА           |  |

| Common-Mode Voltage Range         | $V_{CM}$                 | V <sub>S</sub> =5.5V                            |              |            | -0.1~+5.6                                        |       | V            |  |

| Common-Mode Rejection Ratio       | CMRR                     | $V_S$ =5.5V, $V_{CM}$ =-0.1\                    | /~4V         | 75         | 90                                               | 90 dB |              |  |

|                                   |                          | (Note)                                          |              | 73         |                                                  |       | ub ub        |  |

|                                   |                          | $V_S$ =5.5V, $V_{CM}$ =-0.1\                    | /~5.6V       | 66         | 92                                               |       | dB           |  |

|                                   |                          | (Note)                                          |              | 64         |                                                  |       | ub           |  |

|                                   |                          | $R_L = 600\Omega$ , $Vo = 0.15$                 | /~4.85V      | 92         | 100                                              |       | dB           |  |

| Open-Loop Voltage Gain            | $A_OL$                   | (Note)                                          |              | 78         |                                                  |       | ub ub        |  |

| open zeep venage eam              | 7 .OL                    | $R_L=10K\Omega$ , $Vo=0.05$                     | √~4.95V      | 100        | 110                                              |       | dB           |  |

|                                   |                          | (Note)                                          |              | 82         |                                                  |       |              |  |

| Input Offset Voltage Drift        | $\Delta V_{OS}/\Delta_T$ |                                                 |              | 2.7        |                                                  |       | μV/°C        |  |

| OUTPUT CHARACTERISTICS            |                          | 1                                               |              | 1          | 1                                                |       | 1            |  |

| Output Voltage Swing from Rail    | Vo                       | R <sub>L</sub> =600Ω                            |              |            | 0.1                                              |       | V            |  |

| Catput Voltage Ching II chi i tai |                          | R <sub>L</sub> =10KΩ                            |              |            | 0.015                                            |       |              |  |

| Output Current                    | I <sub>OUT</sub>         |                                                 |              | 45         | 48                                               | mA    |              |  |

| ·                                 |                          | (Note)                                          |              | 30         |                                                  |       | _            |  |

| Closed-Loop Output Impedance      | Ro                       | F=100KHz, G=+1                                  |              |            | 2.6                                              |       | Ω            |  |

| POWER SUPPLY                      |                          | +                                               |              | 1 -        | 1                                                |       | 1            |  |

| Operating Voltage Range           | Vs                       |                                                 |              | 2.5        |                                                  | 5.5   | V            |  |

| 1 0 0 0                           |                          | (Note)                                          | 1            | 2.5        |                                                  | 5.5   |              |  |

| Power Supply Rejection Ratio      | PSRR                     | V <sub>S</sub> =+2.5V~+5.5V,                    |              | 79         | 94                                               |       | dB           |  |

| 117                               |                          | V <sub>CM</sub> =(-V <sub>S</sub> )+0.5V        | (Note)       | 76         |                                                  |       |              |  |

| Quiescent Current/ Amplifier      | IQ                       | I <sub>OUT</sub> =0                             |              |            | 250                                              | 400   | μA           |  |

| ·                                 |                          |                                                 | (Note)       |            |                                                  | 480   |              |  |

| DYNAMIC PERFORMANCE               |                          | a                                               |              |            |                                                  |       |              |  |

| Gain-Bandwidth Product            | GBP                      | R <sub>L</sub> =10KΩ                            |              |            | 3                                                |       | MHz          |  |

| Phase Margin                      | φο                       |                                                 |              |            | 67                                               |       | degrees      |  |

| Full Power Bandwidth              | BW <sub>P</sub>          | <1% distortion, R <sub>L</sub> =600Ω            |              |            | 50                                               |       | KHz          |  |

| Slew Rate                         | SR                       | G=+1, 2V Step, R <sub>L</sub> =10KΩ             |              |            | 1.7                                              |       | V/µs         |  |

| Settling Time To 0.1%             | t <sub>S</sub>           | G=+1, 2V Step, R <sub>L</sub> =600Ω             |              | 1          | 2.1                                              |       | μs           |  |

| Overload Recovery Time            | t <sub>OR</sub>          | V <sub>IN</sub> · Gain=Vs, R <sub>L</sub> =600Ω |              |            | 1                                                |       | μs           |  |

| NOISE PERFORMANCE                 |                          | 1                                               |              | 1          | <del>                                     </del> |       | <del>-</del> |  |

| Voltage Noise Density             | e <sub>N</sub>           | f=1kHz                                          |              |            | 12                                               |       | nV/ √Hz      |  |

| Current Noise Density             | I <sub>N</sub>           | f=1kHz                                          |              |            | 3                                                |       | fA/ √Hz      |  |

| Note: Denotes the specifications  | which apply o            | over the operating tem                          | perature rar | nge (-40°0 | C~125°C).                                        |       |              |  |

#### APPLICATION NOTES

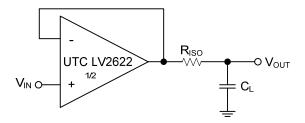

#### **Driving a Capacitive Load**

The UTC **LV2622** can directly drive 1000pF in unity-gain without oscillation. The unity-gain follower (buffer) is the most sensitive configuration to capacitive loading. When the amplifier is configured in this manner, capacitive loading directly on the output will decrease the device's phase margin leading to high frequency ringing or oscillations. It is recommended that an isolation resistor ( $R_{\rm ISO}$ ) is placed in series with the output of the amplifier when the greater capacitive load is required. The circuit is shown in Figure 1. The  $R_{\rm ISO}$  and the load capacitor  $C_L$  form a zero to increase stability, but this method results in a loss of gain accuracy for  $R_{\rm ISO}$  dividing the voltage with  $R_{\rm LOAD}$ .

Figure 1. Indirectly Driving Heavy Capacitive Load

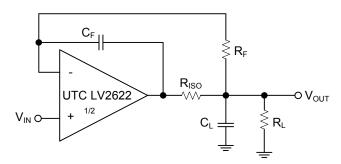

The circuit in Figure 2 provides DC accuracy and AC stability. To increase the DC accuracy,  $R_F$  should be connected between the inverting input and the output. To preserve the phase margin in the overall feedback loop,  $C_F$  is required and can compensate the loss of phase margin together with  $R_{Iso}$  by feeding the high frequency component of the output signal back to the amplifier's inverting input

Figure 2. Indirectly Driving Heavy Capacitive Load with DC Accuracy

For no-buffer configuration, there are two others ways to increase the phase margin: (a) by increasing the amplifier's gain or (b) by placing a capacitor in parallel with the feedback resistor to counteract the parasitic capacitance associated with inverting node.

#### ■ APPLICATION NOTES(Cont.)

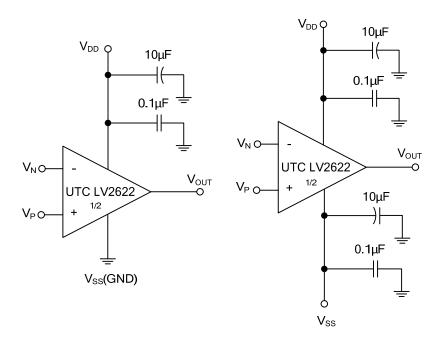

#### **Power-Supply Bypassing and Layout**

The UTC **LV2622** can apply for a single +2.5V $\sim$ +5.5V supply or dual ±1.25V $\sim$ ±2.75V supplies. For single-supply operation, a 0.1 $\mu$ F ceramic capacitor should be placed close to the V<sub>DD</sub> pin to bypass the power supply V<sub>DD</sub>. For dual-supply operation, separate 0.1 $\mu$ F ceramic capacitors should be placed to the V<sub>DD</sub> and the V<sub>SS</sub> supplies to bypass them to ground, and 2.2 $\mu$ F tantalum capacitor for better performance.

By decreasing the amount of stray capacitance at the op amp's inputs and output, PC board I performance can be optimized. For example, placing external components as close to the device as possible can minimize trace lengths and widths. and using surface-mount components is a better way.

For the operational amplifier, soldering the part to the board directly is strongly recommended. The EMI can be minimized because keeping the high frequency big current loop area small.

Figure 3. Amplifier with Bypass Capacitors

#### Grounding

A ground plane layer is important for UTC **LV2622** circuit design. The length of the current path speed currents in an inductive ground return will create an unwanted voltage noise. Broad ground plane areas will reduce the parasitic inductance.

#### **Input-to-Output Coupling**

The input and output signal traces should not be parallel to minimize capacitive coupling. This helps reducing unwanted positive feedback.

#### **TYPICAL APPLICATION CIRCUITS**

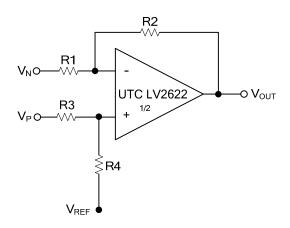

Figure 4. Differential Amplifier

Figure 4 is the differential amplifier. If the resistors ratios are equal (R4/R3=R2/R1), then V<sub>OUT</sub>=(Vp-Vn)×R2/R1+Vref.

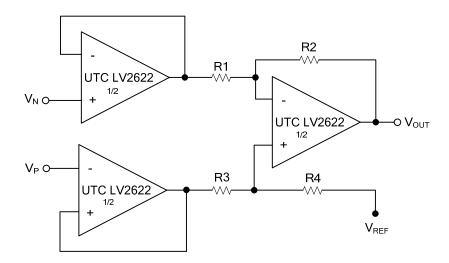

Figure 5. Instrumentation Amplifier

Figure 5 performs the same function as that in Figure 4 but with the high input impedance.

#### ■ TYPICAL APPLICATION CIRCUITS(Cont.)

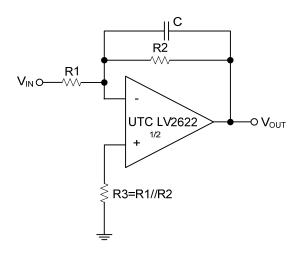

Figure 6. Low Pass Active Filter

Figure 6 is the low pass filter. It's DC gain is -R2/R1 and the -3dB corner frequency is  $1/2\pi R_2C$ .

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.