**UTC** UNISONIC TECHNOLOGIES CO., LTD

# M7085

# PFM STEP-DOWN DC-DC CONTROLLER

### DESCRIPTION

The UTC M7085 step-down DC-DC Controller is optimized for use with a power PMOSFET. It utilize a Pulse-Frequency Modulation (PFM) control scheme that implies high efficiency operation at light loads.

There are two user-selectable over-current protection methods one provides over-current protection by taking advantage of the RDS(ON) of the P- Channel. The other provides accurate over-current protection with the use of an external sense resistor. The cycle-by-cycle current limit threshold can be adjusted with a external resistor.

### **FEATURES**

- \* High efficiency 90% and up is possible

- \* Low dropout operation: 100% duty cycle

- \* Maximum operating frequency > 1MHz

- \* Two methods of over-current protection

- \* 4.5V ~ 35V wide input range

- \* 1.24V ~ VIN adjustable output range

#### **ORDERING INFORMATION**

| Ordering Number |              | Deekeese | Decking   |  |

|-----------------|--------------|----------|-----------|--|

| Lead Free       | Halogen Free | Package  | Packing   |  |

| M7085L-SM1-R    | M7085G-SM1-R | MSOP-8   | Tape Reel |  |

| M7085L-SM1-T    | M7085G-SM1-T | MSOP-8   | Tube      |  |

| M7085L-SM1-R<br>(1)Packing Type<br>(2)Package Type<br>(3)Lead Free | (1) R: Tape Reel, T: Tube<br>(2) SM1: MSOP-8<br>(3) G: Halogen Free, L: Lead Free |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------|

# M7085

2 of 7

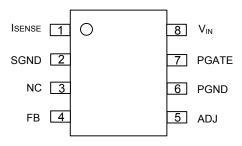

### **PIN CONFIGURATION**

#### **PIN DESCRIPTION**

| PIN NO | PIN NAME           | DESCRIPTION                                                                                      |

|--------|--------------------|--------------------------------------------------------------------------------------------------|

| 1      | I <sub>SENSE</sub> | The over-current protection input pin that be connected to Drain node of the external P-Channel. |

| 2      | $S_{GND}$          | Signal Ground.                                                                                   |

| 3      | NC                 | No Connection.                                                                                   |

| 4      | FB                 | The feedback voltage input.                                                                      |

| 5      | ADJ                | The over-current protection input pin that adjust current limit threshold.                       |

| 6      | $P_{GND}$          | Power Ground.                                                                                    |

| 7      | GATE               | Driver pin to Gate of the external P-Channel. PGATE swings between $V_{IN}$ and $V_{IN}$ -5V.    |

| 8      | V <sub>IN</sub>    | Power Supply                                                                                     |

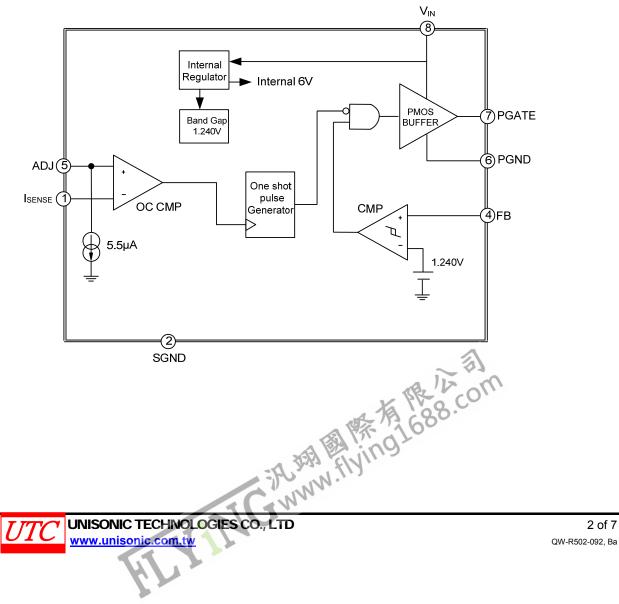

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATING**

| PARAMETER                               | SYMBOL             | RATINGS    | UNIT |  |

|-----------------------------------------|--------------------|------------|------|--|

| Input Voltage                           | V <sub>IN</sub>    | -0.3 ~ 36  | V    |  |

| P <sub>GATE</sub> Voltage               | V <sub>PGATE</sub> | -0.3 ~ 36  | V    |  |

| FB Voltage                              | V <sub>FB</sub>    | -0.3 ~ 5   | V    |  |

| I <sub>SENSE</sub> Voltage              | V <sub>ISNS</sub>  | -1.0 ~ 36  | V    |  |

| ADJ Voltage                             | V <sub>ADJ</sub>   | -0.3 ~ 36  | V    |  |

| Power Dissipation (T <sub>A</sub> =25℃) | PD                 | 400        | mW   |  |

| Junction Temperature                    | TJ                 | 150        | °C   |  |

| Storage Temperature                     | T <sub>STG</sub>   | -65 ~ +150 | °C   |  |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

#### **OPERATING RATINGS**

| PARAMETER                      | SYMBOL           | RATINGS    | UNIT |

|--------------------------------|------------------|------------|------|

| Supply Voltage                 |                  | 4.5 ~ 35   | V    |

| Operating Junction Temperature | T <sub>OPR</sub> | -40 ~ +125 | °C   |

#### **ELECTRICAL CHARACTERISTICS**

| PARAMETER                             | SYMBOL                  | TEST CONDITIONS                                                                  | MIN   | TYP   | MAX   | UNIT |

|---------------------------------------|-------------------------|----------------------------------------------------------------------------------|-------|-------|-------|------|

| Feedback Voltage (Note 1)             | V <sub>FB</sub>         |                                                                                  | 1.224 | 1.240 | 1.256 | V    |

|                                       |                         |                                                                                  | 1.215 |       | 1.265 |      |

| Minimum Driver Voltage                | VPGATE(MIN)             | $V_{IN}$ = 4.5V $V_{FB}$ = 1.0V<br>$I_{GATE}$ = 100µA sink                       |       | 1.15  |       | V    |

| Comparator Hysteresis                 | V <sub>HYS</sub>        |                                                                                  |       | 10    | 16    | mV   |

|                                       | VHYS                    |                                                                                  |       | 15    | 21    |      |

| Current Limit Comparator Trip Voltage | V <sub>CL</sub> (Note2) | R <sub>ADJ</sub> = 20Ω                                                           |       | 110   |       | mV   |

|                                       |                         | R <sub>ADJ</sub> = 160Ω                                                          |       | 880   |       |      |

| Current Limit Comparator Offset       | V <sub>CL(OFF)</sub>    | V <sub>FB</sub> = 1.5V                                                           | -20   | 0     | +20   | mV   |

| Current Limit ADJ Current Source      | I <sub>CL(ADJ)</sub>    | V <sub>FB</sub> = 1.5V                                                           | 3.0   | 5     | 7.0   | μA   |

| FB pin Bias Current (Note 3)          | I <sub>FB</sub>         | V <sub>FB</sub> = 1.0V                                                           |       | 320   | 756   | nA   |

| Driver Output Current Source          | - I <sub>PGATE</sub>    | V <sub>IN</sub> = 7V, P <sub>GATE</sub> = 3.5V                                   |       | 0.4   |       | A    |

| Driver Output Current Sink            |                         | V <sub>IN</sub> = 7V, P <sub>GATE</sub> = 3.5V                                   |       | 0.3   |       |      |

| Driver Registeres                     | R <sub>PGATE</sub>      | I <sub>SOURCE</sub> = 100mA                                                      |       | 5     |       | Ω    |

| Driver Resistance Sink                |                         | I <sub>SINK</sub> = 100mA                                                        |       | 8     |       |      |

| Current Limit One Shot off Time       | T <sub>CL</sub>         | V <sub>ADJ</sub> = 11.5V, V <sub>ISNS</sub> = 11.0V,<br>V <sub>FB</sub> = 1.0V   | 5     | 8     | 13    | μS   |

| Minimum on Time in Normal Operation   | T <sub>OPR(MIN)</sub>   | $V_{ISNS} = V_{ADJ}$ +0.1V, $C_{LOAD}$ on<br>OUT = 1000pF, (Note 4)              |       | 110   |       | ns   |

| Minimum on Time in Current Limit      | T <sub>CL(MIN)</sub>    | $V_{ISNS} = V_{ADJ}$ +0.1V, $V_{FB} = 1.0V$<br>$C_{LOAD}$ on OUT=1000pF (Note 4) |       | 185   |       | ns   |

| Feedback Voltage Line Regulation      | $V_{FB}/ V_{IN}$        | $4.5 \le V_{IN} \le 35V$                                                         |       | 0.010 |       | %/V  |

| Quiescent Current at Ground Pin       | lq                      | FB = 1.5V (Not Switching)                                                        |       | 300   | 500   | μA   |

Note: 1. The V<sub>FB</sub> is the trip voltage at the FB pin when PGATE switches from high to low. -iLiter Entrate 1688.com

2.  $V_{CL}$  =  $I_{CL_{ADJ}} * R_{ADJ}$

- 3. Bias current flows out from the FB pin.

- 4. A 1000pF capacitor is connected between  $V_{IN}$  and  $P_{GATE}$ .

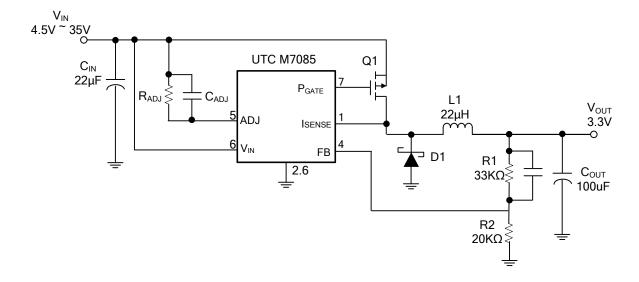

# TYPICAL APPLICATION CIRCUIT

# M7085

# **APPLICATION INFORMATION**

### Setting the output voltage

Select an output voltage between 1.24V and VIN by connecting FB to a resistive voltage-divider between VOUT and GND (see the Typical Operating Circuit). Choose R2 for a reasonable bias current in the resistive divider. A wide range of resistor values is acceptable.

R1, R2 is given by:

$$V_{OUT} = 1.240^{*} (R1 + R2) / R2$$

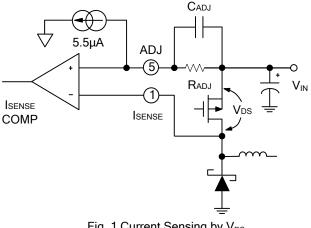

## Setting over current protection threshold by the RDS(ON) of the P-Channel

The UTC M7085 has a cycle-by-cycle current limit. Current limit is sensed across the V<sub>DS</sub> of the P-Channel or across an additional sense resistor. When current limit is activated, the UTC M7085 turns off the external P-Channel for a period of 9µs(typical). The current limit is adjusted by an external resistor, RADJ.

The current limit circuit is composed of the I<sub>SENSE</sub> comparator and the one-shot pulse generator. The positive input of the I<sub>SENSE</sub> comparator is the ADJ pin. An internal 5.5µA current sink creates a voltage across the external R<sub>ADJ</sub> resistor. This voltage is compared to the voltage across the P-Channel or sense resistor. The ADJ voltage can be calculated as follows:

$$V_{ADJ} = V_{IN} - (R_{ADJ} * 3.0 \mu A)$$

Where  $3.0\mu A$  is the minimum  $I_{CL(ADJ)}$  value.

The negative input of the I<sub>SENSE</sub> comparator is the I<sub>SENSE</sub> pin that should be connected to the drain of the external P-Channel. The inductor current is determined by sensing the V<sub>DS</sub>. It can be calculated as follows.

$V_{ISENSE} = V_{IN} - (R_{DS(ON)} * I_{IND PEAK}) = V_{IN} - V_{DS}$

Fig. 1 Current Sensing by V<sub>DS</sub>

The current limit is activated when the voltage at the ADJ pin exceeds the voltage at the I<sub>SENSE</sub> pin. The I<sub>SENSE</sub> comparator triggers the 9µs one shot pulse generator forcing the driver to turn the P-Channel off. The driver turns the P-Channel back on after 9µs. If the current has not reduced below the set threshold, the cycle will repeat continuously.

A filter capacitor, CADJ, should be placed as shown in Fig. 1 CADJ filters unwanted noise so that the ISENSE comparator will not be accidentally triggered. A value of 100pF to 1nF is recommended in most applications. Higher values can be used to create a soft-start function. The current limit comparator has approximately 100ns of blanking time. This ensures that the P-Channel is fully on when the current is sensed. However, under extreme conditions such as cold temperature, some P-Channels may not fully turn on within the blanking time. In this case, the current limit threshold must be increased. If the current limit function is used, the on time must be greater than 100ns. Under low duty cycle operation, the maximum operating frequency will be limited by this minimum on time.

# APPLICATION INFORMATION(Cont.)

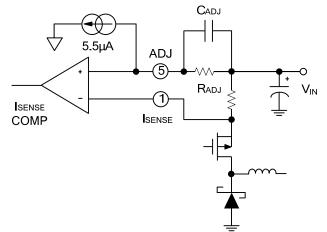

### Setting over current protection threshold by external sense resistor

The  $V_{DS}$  of a P-Channel will tend to vary significantly over temperature. This will result an equivalent variation in current limit. To improve current limit accuracy an external sense resistor can be connected from  $V_{IN}$  to the source of the P-Channel, as shown in Fig. 2.

Fig. 2 Current Sensing by External Resistor

## Setting start up time

The current limit circuit is active during start-up. During start-up the P-Channel will stay on until either the current limit or the feedback comparator is tripped If the current limit comparator is tripped first then the fold back characteristic should be taken into account. Start-up into full load may require a higher current limit set point or the load must be applied after start-up.

One problem with selecting a higher current limit is inrush current during start-up. Increasing the capacitance( $C_{ADJ}$ ) in parallel with  $R_{ADJ}$  results in soft-start.  $C_{ADJ}$  and  $R_{ADJ}$  create an RC time constant forcing current limit to activate at a lower current. The output voltage will ramp more slowly when using the soft-start functionality. There are example start-up plots for  $C_{ADJ}$  equal to 1nF and 10nF in the Typical Performance Characteristics. Lower values for  $C_{ADJ}$  will have little to no effect on soft-start.

# Inductor selection (L1)

UTC **M7085** operates over a wide frequency range and can use a wide range of inductance values. The inductance value and the resulting ripple is one of the key parameters controlling operating frequency. The second is the ESR.

# Output capacitor selection (COUT)

The output capacitor,  $C_{OUT}$ , is required to keep the output voltage ripple small and to ensure regulation loop stability.  $C_{OUT}$  must have low impedance at the switching frequency. For most applications, a 200mF capacitor is sufficient.

# Input capacitor selection (C<sub>IN</sub>)

The input capacitor,  $C_{IN}$ , reduces the current peaks drawn and reduces switching noise in the IC. a bypass capacitor is required between the input source and ground. It must be located near the source pin of the external P-Channel. The input capacitor prevents large voltage transients at the input and provides the instantaneous current when the P-Channel turns on. The capacitance value should be selected such that the ripple voltage created by the charge and discharge of the capacitance is less than 10% of the total ripple across the capacitor.

### Catch diode selection (D1)

The important parameters for the catch diode are the peak current, the peak reverse voltage, and the average power dissipation. For high temperature applications, diode leakage current may become significant and require a higher reverse voltage rating to achieve acceptable performance.

# APPLICATION INFORMATION(Cont.)

## P-Channel MOSFET Selection(Q1)

An external P-Channel power MOSFET must be used the UTC **M7085** key selection criteria for the power for the P-Channel are the maximum Drain-Source voltage ( $V_{DS}$ ) MOSFET are the gate threshold,  $V_{GS}$ , the "ON" resistance,  $R_{DS(ON)}$  and its total gate charge.

The voltage across the PFET when it is turned off is equal to the sum of the input voltage and the diode forward voltage. The  $V_{DS}$  must be selected to provide some margin beyond the input voltage.

R<sub>DS(ON)</sub>determines the conduction losses for each switching cycle, the lower the ON resistance, the higher the efficiency can be chivied.

A power MOSFET with lower gate charge can give lower switching losses but the fast transient can cause unwanted EMI to the system. Compromise in between is required during the design stage. Keeping the gate capacitance below 2000pF is recommended.

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.