# PA3212

# 2.6W STEREO AUDIO AMPLIFIER WITH FOUR SELECTABLE GAIN SETTINGS AND MUX CONTROL

#### DESCRIPTION

As operating on a single 5V supply, the UTC **PA3212** is capable of delivering 2.6W of output power per channel into  $3\Omega$  loads. In Bridge-Tied Load (BTL) mode the UTC **PA3212** has less than 1% THD+N, and it also has less than 0.65% THD+N across its specified frequency range when driving 1 W into 8- $\Omega$  speakers.

Way of two terminals (GAIN0 and GAIN1) can configure and control the amplifier gain. It also provides BTL gain settings of 2, 6, 12 and 24 V/V.

Other features included that the SHDN mode is provided to disable UTC **PA3212** for the low current consumption applications and the current consumption can be reduced to typically 150µA.

## FEATURES

- \* Output power at 0.65% THD+N, V<sub>DD</sub>=5V(TYP)

- -2.6W/CH (typical) into a 3 $\Omega$  load

- -1.0W/CH (typical) into a 8Ω load \* Bridge-tied load (BTL) supported

- \* Gain control internally

- \* Gain control internally

- \* Differential Input fully

- \* Depop circuitry Inside

- \* Shutdown protection

- \* Stereo input

## ORDERING INFORMATION

| Ordering      | Number        | Dookogo   | Packing   |  |

|---------------|---------------|-----------|-----------|--|

| Lead Free     | Halogen Free  | Package   |           |  |

| PA3212L-N24-R | PA3212G-N24-R | HTSSOP-24 | Tape Reel |  |

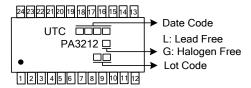

#### MARKING

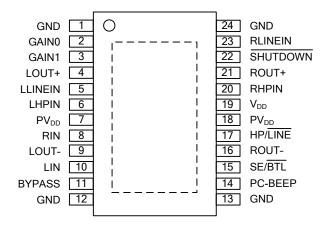

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTION**

| PIN NO.    | PIN NAME          | I/O | DESCRIPTION                                                                                                                                |

|------------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1,12,13,24 | GND               |     | Ground.                                                                                                                                    |

| 11         | BYPASS            |     | Connected to voltage divider                                                                                                               |

| 2          | GAIN0             | Ι   | For gain control: Bit 0                                                                                                                    |

| 3          | GAIN1             | -   | For gain control: Bit 1                                                                                                                    |

| 5          | LLINEIN           | -   | Line input for Left channel, available when pin15 is held low.                                                                             |

| 6          | LHPIN             | -   | Headphone input Left channel, available when pin15 is held high.                                                                           |

| 7,18       | PV <sub>DD</sub>  | Ι   | Power supply voltage.                                                                                                                      |

| 8          | RIN               | Ι   | Differential input for right channel. And for single-ended inputs is also AC ground.                                                       |

| 10         | LIN               | Ι   | Differential input for Left channel. And for single-ended inputs is also AC ground.                                                        |

| 14         | PC-BEEP           | I   | PC-BEEP mode input. When at least eight continuous >1-V <sub>PP</sub> square waves is input to this pin, PC-BEEP is enabled.               |

| 17         | HP/LINE           | Ι   | Input of MUX control. Being high to select the inputs of Pin6, 20, and low to select inputs of PIN 5, 23.                                  |

| 15         | SE/BTL            | I   | Low for BTL mode, high for SE mode.                                                                                                        |

| 19         | V <sub>DD</sub>   | Ι   | Analog V <sub>DD</sub> supply voltage                                                                                                      |

| 20         | RHPIN             | Ι   | Right channel headphone input, selected when pin17 is held high.                                                                           |

| 23         | RLINEIN           | I   | Headphone input right channel, available when pin17 is held low.                                                                           |

| 22         | SHUTDOWN          | Ι   | In shutdown mode when held low, expect PC-BEEP remains active.                                                                             |

| 4          | L <sub>OUT+</sub> | 0   | In BTL mode: left channel + output; In SE mode: left channel + output                                                                      |

| 9          | L <sub>OUT-</sub> | 0   | In BTL mode: left channel - output; In SE mode: high impedance                                                                             |

| 16         | R <sub>OUT-</sub> | 0   |                                                                                                                                            |

| 21         | R <sub>OUT+</sub> | 0   | In BTL mode: right channel - output; In SE mode: high impedance                                                                            |

|            |                   |     | In BTL mode: right channel + output; In SE mode: right channel + output<br>In BTL mode: right channel - output; In SE mode: high impedance |

|            |                   |     | <b>ES CO., LTD</b> 2 of 9<br>QW-R502-310.B                                                                                                 |

# PA3212

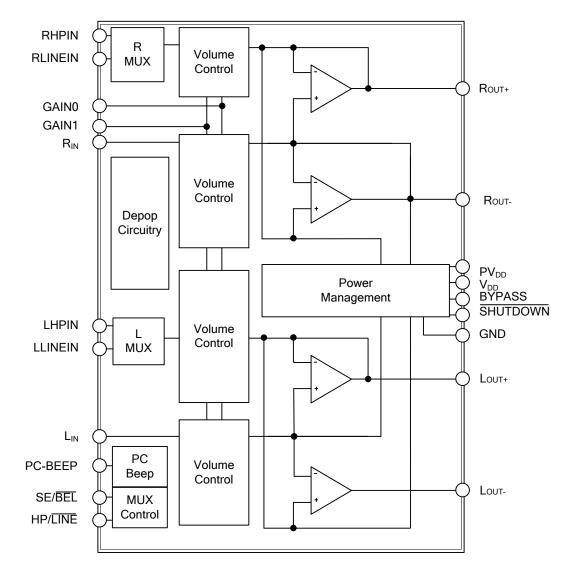

## BLOCK DIAGRAM

## ABSOLUTE MAXIMUM RATING

| PARAMETER             | SYMBOL           | RATINGS                       | UNIT |

|-----------------------|------------------|-------------------------------|------|

| Supply Voltage        | V <sub>DD</sub>  | 6                             | V    |

| Input Voltage         | V <sub>IN</sub>  | -0.3 ~ V <sub>DD</sub> ~ +0.3 | V    |

| Junction Temperature  | TJ               | +150                          | °C   |

| Operating Temperature | T <sub>OPR</sub> | -40 ~ +85                     | °C   |

| Storage Temperature   | T <sub>STG</sub> | -55 ~ +150                    | С°   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

### ■ ELECTRICAL CHARACTERISTICS (T<sub>a</sub>= 25°C, unless otherwise specified.)

| PARAMETER                            | SYMBOL                 | TEST CONDITIONS                                        | MIN                 | TYP  | MAX                 | UNIT                 |  |

|--------------------------------------|------------------------|--------------------------------------------------------|---------------------|------|---------------------|----------------------|--|

| DC ELECTRICAL CHARACTERISTICS        |                        |                                                        |                     |      |                     |                      |  |

| Supply Voltage                       | $V_{\text{DD}}$        |                                                        | 4.5                 | 5    | 5.5                 | V                    |  |

| High-Level Input voltage             | VIH                    | SHUTDOWN                                               | 2                   |      |                     | V                    |  |

|                                      |                        | SE/BTL, HP/LINE, GAIN0, GAIN1                          | 0.8×V <sub>DD</sub> |      |                     | V                    |  |

|                                      | VIL                    | SHUTDOWN                                               |                     |      | 0.8                 | V                    |  |

| Low-Level Input voltage              |                        | GAIN0, GAIN1                                           |                     |      | $0.4 \times V_{DD}$ | V                    |  |

|                                      |                        | SE/BTL, HP/LINE                                        |                     |      | $0.6 \times V_{DD}$ | V                    |  |

| DC Differential Output Voltage       | V <sub>OUT(DIFF)</sub> | V <sub>IN</sub> =0V,Gain=2V/V                          |                     |      | 25                  | mV                   |  |

| Supply Current in Mute Mede          | I <sub>DD</sub>        | BTL Mode                                               |                     | 6    | 8                   | mA                   |  |

| Supply Current in Mute Mode          |                        | SE Mode                                                |                     | 3    | 4                   | mA                   |  |

| Supply Current, Shutdown Mode        | I <sub>DD(SD)</sub>    | V <sub>DD</sub> =5V                                    |                     | 150  | 300                 | μA                   |  |

| High-Level Input Current             | I <sub>IH</sub>        | $V_{DD}=5.5V, V_{IN}=V_{DD}$                           |                     |      | 900                 | nA                   |  |

| Low-Level Input Current              | I <sub>IL</sub>        | $V_{DD}=5.5V, V_{IN}=0V$                               |                     |      | 900                 | nA                   |  |

| Operating Free-Air Temperature       | T <sub>A</sub>         |                                                        | -40                 |      | +85                 | °C                   |  |

| AC ELECTRICAL CHARACTERISTI          | CS (VDD =              | 5.0V, RL = 8 $\Omega$ , unless otherwise no            | oted)               |      |                     |                      |  |

| Output Power                         | Pout                   | THD=1%, BTL, R <sub>L</sub> =3Ω, G=2V/V                |                     | 2.05 |                     | W                    |  |

|                                      |                        | THD=10%, BTL, R <sub>L</sub> =3Ω, G=2V/V               |                     | 2.6  |                     |                      |  |

| Total Harmonic Distortion Plus Noise | THD+N                  | P <sub>OUT</sub> =1W, BTL, R <sub>L</sub> = 8Ω, G=2V/V |                     | 0.65 |                     | %                    |  |

| Max Output Power Bandwidth           | B <sub>OM</sub>        | THD= 5%                                                |                     | 15   |                     | kHz                  |  |

| Power Supply Ripple Rejection        | PSRR                   | f=1kHz, BTL, G=2V/V, C <sub>BYP</sub> =0.47µF          |                     | 72   |                     | dB                   |  |

| Output Noise Voltage                 | eN                     | C <sub>BYP</sub> =0.47µF,BTL, G=2V/V                   |                     | 20   |                     | $\mu V_{\text{RMS}}$ |  |

|                                      | EIN                    | C <sub>BYP</sub> =0.47µF, SE, G=2V/V                   |                     | 18   |                     | $\mu V_{\text{RMS}}$ |  |

| Signal-to-Noise Ratio                | SNR                    |                                                        |                     | 105  |                     | dB                   |  |

Note: Output power is measured at the output terminals of the IC at 1kHz.

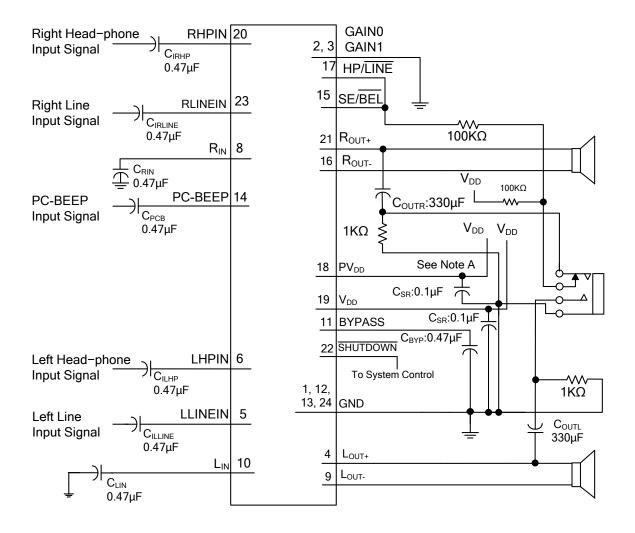

### TYPICAL APPLICATION CIRCUITS

A 0.1- $\mu$ F ceramic capacitor should be placed very close to the IC. A larger electrolytic capacitor of 10  $\mu$ F or greater should be placed near the audio power amplifier for filtering lower frequency noise signals, .

Typical PA3212 Application Circuit Using Single-Ended Inputs and Input MUX

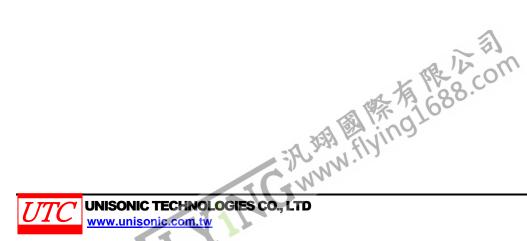

## **TYPICAL APPLICATION CIRCUITS(Cont.)**

A 0.1- $\mu$ F ceramic capacitor should be placed as close as possible to the IC. A larger electrolytic capacitor of 10  $\mu$ F or greater should be placed near the audio power amplifier for filtering lower frequency noise signals.

Typical PA3212 Application Circuit Using Differential Inputs

### APPLICATION INFORMATION

#### Shutdown Mode Operating

| INPUT   |        |          | AMPLIFIER |        |

|---------|--------|----------|-----------|--------|

| HP/LINE | SE/BTL | SHUTDOWN | INPUT     | OUTPUT |

| Х       | Х      | L        | Х         | MUTE   |

| L       | L      | Н        | LINE      | BTL    |

| L       | Н      | Н        | LINE      | SE     |

| Н       | L      | Н        | HEADPHONE | BTL    |

| Н       | Н      | Н        | HEADPHONE | SE     |

X: Don't care L: Low

H: High

#### C<sub>I</sub> (Input Capacitor)

The value of  $C_1$  is important to consider as it directly affects the bass performance of the application circuit. When  $C_1$  is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation, it's value can be calculate by this equation:

$\begin{array}{l} C_{i}{=}1/(2\pi R_{i}F_{C})\\ R_{i}{:} \ Input \ Impedance\\ F_{C}{:} \ High-pass \ Filter's \ Frequency \end{array}$

The low leakage tantalum or ceramic capacitors are suggested to be used as the input coupling capacitors, because of the small leakage current of the input capacitors will cause the dc offset voltage at the input to the amplifier that reduces the operation headroom, especially at the high gain applications. It is important to let the positive side connecting to the higher dc level of the application when using the polarized capacitors.

#### Gain setting (VS Gain0, Gain1 and R<sub>I</sub>)

Gain setting is determined by GAIN0 and GAIN1. The gains listed in the next table are realized by changing the taps on the input resistors inside the amplifier which will cause the internal input impedance ( $R_{I}$ ) to be dependent on the gain setting as we can see listed in the next table.

| GAIN0 | GAIN1 | R <sub>I</sub> (kΩ) | A <sub>V</sub> (V/V) | SE/BTL |

|-------|-------|---------------------|----------------------|--------|

| 0     | 0     | 91                  | 2                    | 0      |

| 0     | 1     | 45.5                | 6                    | 0      |

| 1     | 0     | 26                  | 12                   | 0      |

| 1     | 1     | 14                  | 24                   | 0      |

| Х     | Х     |                     | 1                    | 1      |

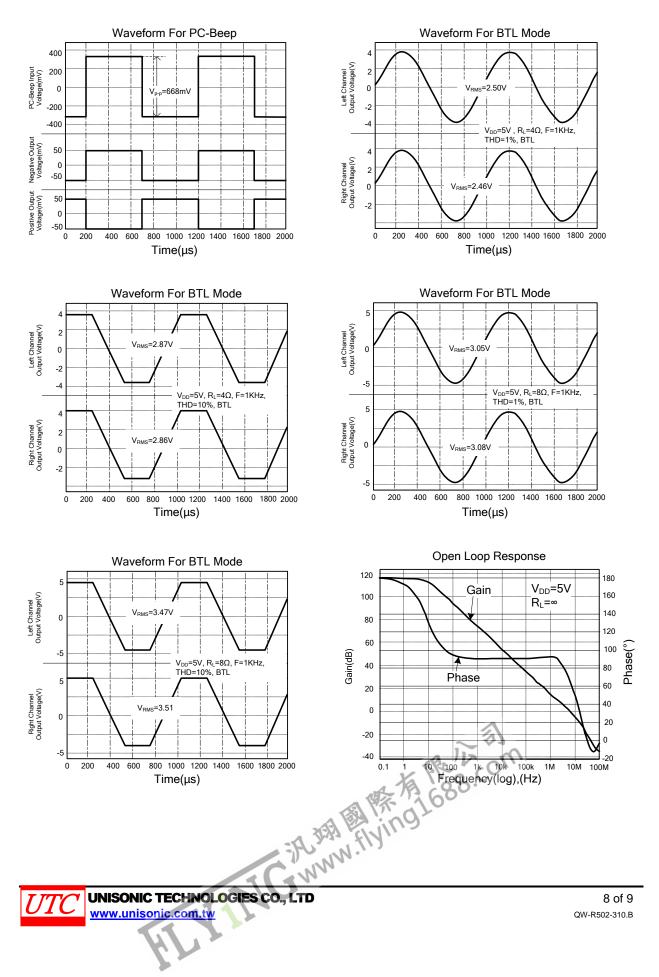

#### TYPICAL CHARACTERISTICS

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.