# **UTC** UNISONIC TECHNOLOGIES CO., LTD

# U74AHCT3G06

# INVERTER WITH OPEN-DRAIN OUTPUT

## DESCRIPTION

The **U74AHCT3G06** is a high-speed Si-gate CMOS device which provides three inverting buffers with open-drain outputs. For digital operation this device must have a pull-up resistor to establish a logic HIGH-level.

The **U74AHCT3G06** is compatible of TTL input switching levels and has supply voltage range from 4.5V to 5.5V.

### FEATURES

- \* Low power supply 1.0µA at 5.5V

- \* Up to 5.5V inputs accept voltages

- \* Low power dissipation

- \* Balanced propagation delays

- \* High noise immunity

- \* Output capability standard (open drain)

#### ORDERING INFORMATION

| Ordering Number    |                    | Packago | Packing   |  |

|--------------------|--------------------|---------|-----------|--|

| Lead Free          | Halogen Free       | Package | Packing   |  |

| U74AHCT3G06L-P08-R | U74AHCT3G06G-P08-R | TSSOP-8 | Tape Reel |  |

#### MARKING

# U74AHCT3G06

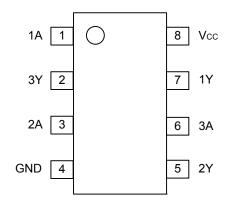

## PIN CONFIGURATION

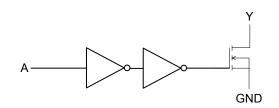

## ■ **FUNCTION TABLE** (each gate)

| INPUT(A) | OUTPUT(Y) |

|----------|-----------|

| L        | Z         |

| Н        | L         |

■ LOGIC DIAGRAM (each gate)

#### ■ ABSOLUTE MAXIMUM RATING (unless otherwise specified)

| PARAMETER                      | SYMBOL           | RATINGS                         | UNIT |

|--------------------------------|------------------|---------------------------------|------|

| Supply Voltage                 | V <sub>cc</sub>  | -0.5 ~ 7.0                      | V    |

| Input Voltage                  | V <sub>IN</sub>  | -0.5 ~ 7.0                      | V    |

| Output Voltage                 | V                | -0.5 ~ 7.0(active mode)         | V    |

| Output Voltage                 | V <sub>OUT</sub> | -0.5 ~ 7.0(high-impedance mode) | V    |

| V <sub>CC</sub> or GND Current | Icc              | ±75                             | mA   |

| Output Current                 | I <sub>OUT</sub> | ±25                             | mA   |

| Input Clamp Current            | I <sub>IK</sub>  | -20                             | mA   |

| Output Clamp Current           | I <sub>OUT</sub> | ±20                             | mA   |

| Operating Temperature          | T <sub>OPR</sub> | -40 ~ + 85                      | °C   |

| Storage Temperature            | T <sub>STG</sub> | -65 ~ + 150                     | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

#### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                | SYMBOL                          | CONDITIONS               | MIN | TYP | MAX | UNIT |

|--------------------------|---------------------------------|--------------------------|-----|-----|-----|------|

| Supply Voltage           | V <sub>CC</sub>                 |                          | 4.5 | 5.0 | 5.5 | V    |

| Input Voltage            | V <sub>IN</sub>                 |                          | 0   |     | 5.5 | V    |

|                          | Vout                            | Active mode              | 0   |     | Vcc | V    |

| Output Voltage           |                                 | High-impedance mode      | 0   |     | 6.0 | V    |

| Input Rise or Fall Times | t <sub>R</sub> , t <sub>F</sub> | $V_{CC} = 5.0 \pm 0.5 V$ |     |     | 20  | ns/V |

#### ■ ELECTRICAL CHARACTERISTICS(T<sub>A</sub>=25°C)

| PARAMETER                           | SYMBOL               | TEST CO                                                                                                   | NDITIONS                | MIN | TYP | MAX   | UNIT |

|-------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------|-------------------------|-----|-----|-------|------|

| High-Level Input Voltage            | VIH                  | V <sub>CC</sub> = 4.5 V to 5.5 V                                                                          |                         | 2.0 |     |       | V    |

| Low-Level Input Voltage             | VIL                  | V <sub>CC</sub> = 4.5 V to 5.5 V                                                                          |                         |     |     | 0.8   | V    |

| Low-Level Output Voltage            | V                    | V <sub>CC</sub> =4.5V,                                                                                    | I <sub>O</sub> = 50 μA  |     | 0   | 0.1   | v    |

|                                     | V <sub>OL</sub>      | $V_{I} = V_{IH} \text{ or } V_{IL}$                                                                       | l <sub>o</sub> = 8.0 mA |     |     | 0.36  | v    |

| Input Leakage Current               | I <sub>I(LEAK)</sub> | $V_1$ = 5.5V or GND, $V_{CC}$ = 0V to 5.5V                                                                |                         |     |     | 0.1   | μA   |

| 3-State output OFF-State Current    | I <sub>OZ</sub>      | $V_{CC}$ =5.5V,V <sub>I</sub> =V <sub>IH</sub> or V <sub>IL</sub> ,V <sub>O</sub> =V <sub>CC</sub> or GND |                         |     |     | ±.025 | μA   |

| Quiescent Supply Current            | Icc                  | $V_{CC}$ =5.5V,V <sub>I</sub> = $V_{CC}$ or GND, $I_0$ = 0                                                |                         |     |     | 1.0   | μA   |

| Additional Quiescent Supply Current | $\Delta I_{CC}$      | V <sub>CC</sub> =5.5V,One input at 3.4V,                                                                  |                         |     |     | 1.35  |      |

|                                     |                      | Other inputs at $V_{CC}$ or GND, $I_{OUT} = 0$                                                            |                         |     |     | 1.35  | mA   |

| Input Capacitance                   | CIN                  | V <sub>I</sub> =V <sub>CC</sub> or GND                                                                    |                         |     | 1.5 | 10    | рF   |

# U74AHCT3G06

## CMOS IC

#### **SWITCHING CHARACTERISTICS** ( $T_A=25^{\circ}C$ , $t_R = t_F \le 3.0 \text{ ns}$ )

| PARAMETER                                        | SYMBOL           | TEST CONDITIONS        |                      | MIN | TYP | MAX | UNIT |

|--------------------------------------------------|------------------|------------------------|----------------------|-----|-----|-----|------|

| Propagation Delay from Input (A) to<br>Output(Y) | t <sub>PZL</sub> |                        | C <sub>L</sub> =15pF | -   | 3.0 | 5.3 | ns   |

|                                                  | t <sub>PLZ</sub> | $V_{CC}$ =4.5V to 5.5V |                      | -   | 3.2 | 4.6 |      |

|                                                  | t <sub>PZL</sub> |                        | C <sub>L</sub> =50pF | -   | 4.2 | 7.5 | -    |

|                                                  | t <sub>PLZ</sub> |                        | CL =30pi             | -   | 4.5 | 7.0 | ns   |

#### ■ OPERATING CHARACTERISTICS (T<sub>A</sub> =25°C)

| PARAMETER                     | SYMBOL          | TEST CONDITIONS                         | TYP | UNIT |

|-------------------------------|-----------------|-----------------------------------------|-----|------|

| Power Dissipation Capacitance | C <sub>PD</sub> | C <sub>L</sub> =50pF, f=1MHz (Note1, 2) | 4.5 | pF   |

Notes

1.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ).

$P_D = C_{PD} \times V_{CC}^2 \times f_i \times N + \Sigma (C_L \times V_{CC}^2 \times f_o)$  where:

$f_i$  = input frequency in MHz;

$f_o$  = output frequency in MHz;

C<sub>L</sub> = output load capacitance in pF;

V<sub>CC</sub> = supply voltage in Volts;

N = number of inputs switching;

$\Sigma(C_L \times V_{CC}^2 \times f_0)$  = sum of the outputs.

2. The condition is  $V_I = GND$  to  $V_{CC}$ .

# U74AHCT3G06

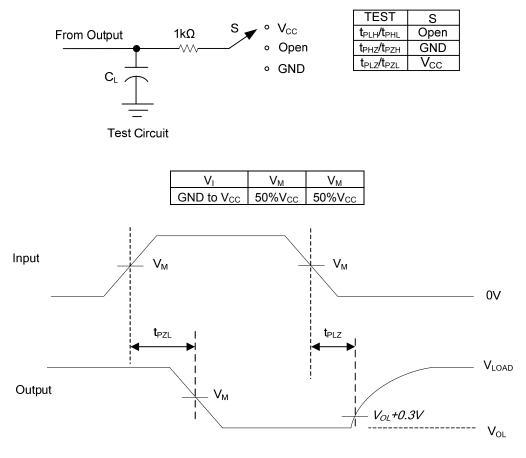

## TEST CIRCUIT AND WAVEFORMS

Voltage Waveforms Enable and Disable Times

Note:  $C_L$  includes probe and jig capacitance.  $P_{RR} \le 1MHz$ ,  $Z_O = 50\Omega$ ,  $t_R \le 3ns$ ,  $t_F \le 3ns$ .

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.