# PHASE LOCKED LOOP WITH VCO

#### DESCRIPTION

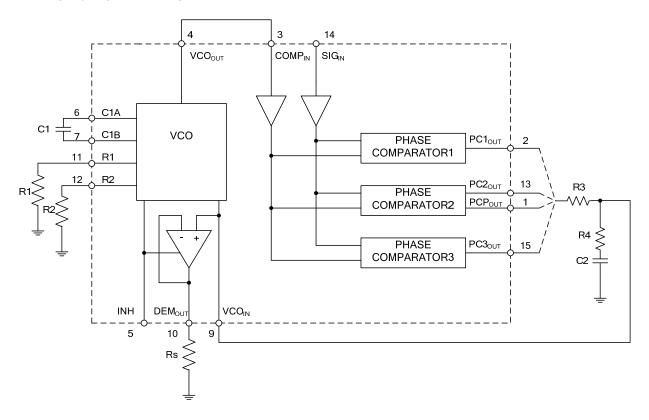

The **U74HC4046A** is a phase-locked-loop circuit including a linear voltage-controlled oscillator (VCO), three different phase comparators (PC1, PC2 and PC3), a common signal input amplifier and a common comparator input.

The signal can be directly coupled to large voltage signals or with a series capacitor coupled to small voltage signals. Small voltage signals can be kept within the linear region of the input amplifiers with a self-bias input circuit. The **U74HC4046A** and a passive low-pass filter form a second-order loop PLL. With a linear op-amp, the VCO achieves excellent linearity.

The VCO requires an external capacitor and resistor. R1 (between R1 and GND) and capacitor C1 (between C1A and C1B) determine the frequency range of the VCO. R2 (between R2 and GND) enables the VCO to have a frequency offset if required.

For the high input impedance of the VCO, the design of low-pass filters is simplified, and the designer has a wide choice of resistor/capacitor ranges. At pin 10 (DEM $_{OUT}$ ), a demodulator output of the VCO input voltage is provided in order not to load the low-pass filter. In conventional techniques, the DEM $_{OUT}$  voltage is one threshold voltage lower than the VCO input voltage, but the DEM $_{OUT}$  voltage of U74HC4046 equals the VCO input voltage. When DEM $_{OUT}$  is used, a load resistor (RS) should be connected from DEM $_{OUT}$  to GND; but if unused, DEM $_{OUT}$  should be left open. The VCO output (VCO $_{OUT}$ ) can be connected directly or via a frequency-divider to the comparator input (COMP $_{IN}$ ). If the VCO input is held at a constant DC level, the VCO output signal has a duty factor of 50% (maximum expected deviation 1%). A LOW level at the inhibit input (INH) enables the VCO and demodulator, while a HIGH level turns both off to minimize standby power consumption.

# **■ FEATURES**

- \* Low Power Consumption

- \* Operating Power Supply Voltage Range: Digital Section 2.0 to 6.0 V

VCO Section 3.0 to 6.0 V

- \* Up to 17 MHz (typ.) Centre Frequency at  $V_{CC}$  = 4.5 V

- \* Excellent VCO Frequency Linearity

- \* VCO-Inhibit Control For ON/OFF Keying and for Low Standby Power Consumption

- \* Minimal Frequency Drift

- \* Three Phase Comparators: EXCLUSIVE-OR;

Edge-Triggered JK Flip-Flop;

Edge-Triggered RS Flip-Flop

- \* Zero Voltage Offset due to OP-Amp Buffering

- \* Standard Output Capability

- \* MSI I<sub>CC</sub> Category

Cwww.flying1688.com

www.unisonic.com.tw 1 of 19

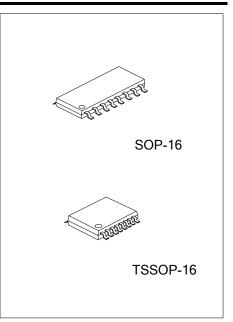

## **ORDERING INFORMATION**

| Ordering          | Number            | Dookogo  | Dooking   |

|-------------------|-------------------|----------|-----------|

| Lead Free         | Halogen Free      | Package  | Packing   |

| U74HC4046AL-S16-R | U74HC4046AG-S16-R | SOP-16   | Tape Reel |

| U74HC4046AL-P16-R | U74HC4046AG-P16-R | TSSOP-16 | Tape Reel |

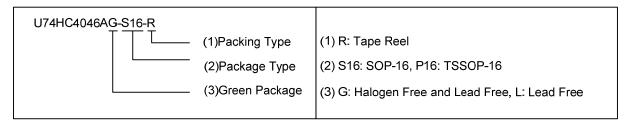

## **MARKING**

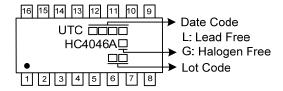

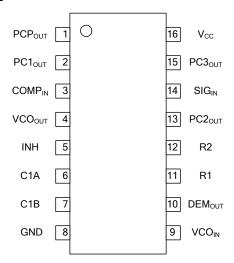

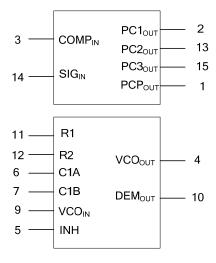

## **■ PIN CONFIGURATION**

## **■ LOGIC SYMBOL**

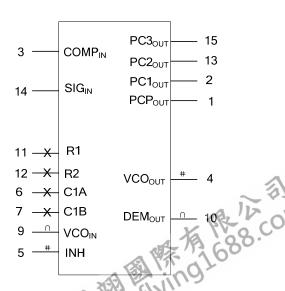

## **■ IEC SYMBOL**

# **PIN DESCRIPTION**

| PIN NO | SYMBOL             | FUNCTION                      |

|--------|--------------------|-------------------------------|

| 1      | PCP <sub>OUT</sub> | Phase comparator pulse output |

| 2      | PC1 <sub>OUT</sub> | Phase comparator 1output      |

| 3      | COMPIN             | Comparator input              |

| 4      | VCO <sub>OUT</sub> | VCO output                    |

| 5      | INH                | Inhibit input                 |

| 6      | C1 <sub>A</sub>    | Capacitor C1 connection A     |

| 7      | C1 <sub>B</sub>    | Capacitor C1 connection B     |

| 8      | GND                | Ground                        |

| 9      | VCOIN              | VCO input                     |

| 10     | DEM <sub>OUT</sub> | Demodulator output            |

| 11     | R1                 | Resistor R1 connection        |

| 12     | R2                 | Resistor R2 connection        |

| 13     | PC2 <sub>OUT</sub> | Phase comparator 2 output     |

| 14     | SIG <sub>IN</sub>  | Signal input                  |

| 15     | PC3 <sub>OUT</sub> | Phase comparator 3 output     |

| 16     | V <sub>CC</sub>    | Positive supply voltage       |

# **■ FUNCTIONAL DIAGRAM**

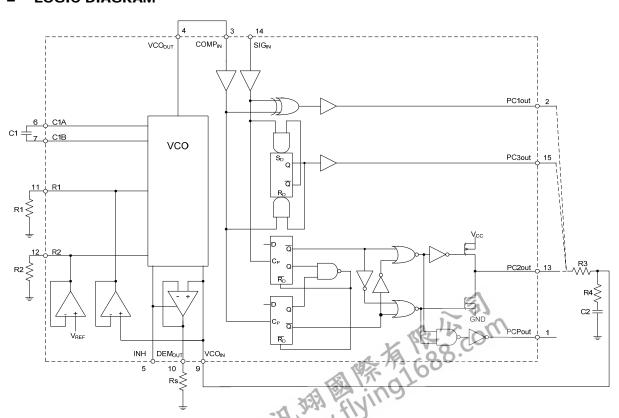

# **■ LOGIC DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                              | SYMBOL                                  | TEST CONDITIONS                                                                   | MIN  | TYP | MAX  | UNIT |

|--------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------|------|-----|------|------|

| DC Supply Voltage                                      | V <sub>CC</sub>                         | TEST SONDITIONS                                                                   | -0.5 |     | +7   | V    |

| DC Input Diode Current                                 | ±l <sub>IK</sub>                        | for $V_{IN} < -0.5 \text{ V}$ or $V_{IN} > V_{CC} + 0.5 \text{ V}$                | 0.0  |     | 20   | mA   |

| DC Output Diode Current                                | ±l <sub>OK</sub>                        | for V <sub>OUT</sub> <-0.5 V or V <sub>OUT</sub> > V <sub>CC</sub> + 0.5 V        |      |     | 20   | mA   |

| DC Output Source or Sink Current                       | ±l <sub>O</sub>                         | for -0.5 V < V <sub>OUT</sub> < V <sub>CC</sub> + 0.5 V                           |      |     | 25   | mA   |

| DC V <sub>CC</sub> or GND Current                      | ±I <sub>CC</sub> ,<br>±I <sub>GND</sub> |                                                                                   |      |     | 50   | mA   |

| Power Dissipation per Package Plastic DIL              |                                         | for temperature range: – 40 to +125 °C above +70 °C: derate linearly with 12 mW/K |      |     | 750  | mW   |

| Power Dissipation per Package<br>Plastic Mini-Pack(SO) | P <sub>D</sub>                          | for temperature range: – 40 to +125 °C above +70 °C: derate linearly with 8 mW/K  |      |     | 500  | mW   |

| Storage Temperature Range                              | T <sub>STG</sub>                        |                                                                                   | -65  |     | +150 | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

## RECOMMENDED OPERATING CONDITIONS

| PARAMETER                                    | SYMBOL           | TEST CONDITIONS         | MIN | TYP | MAX             | UNIT |

|----------------------------------------------|------------------|-------------------------|-----|-----|-----------------|------|

| DC Supply Voltage                            | Vcc              |                         | 3.0 | 5.0 | 6.0             | V    |

| DC Supply Voltage if VCO Section is not used | V <sub>CC</sub>  |                         | 2.0 | 5.0 | 6.0             | V    |

| DC Input Voltage Range                       | V <sub>IN</sub>  |                         | 0   |     | Vcc             | V    |

| DC Output Voltage Range                      | V <sub>OUT</sub> |                         | 0   |     | V <sub>CC</sub> | V    |

|                                              |                  | V <sub>CC</sub> = 2.0 V |     | 6.0 | 1000            | ns   |

| Input Rise and Fall Times (pin 5)            | $t_R$ , $t_F$    | V <sub>CC</sub> = 4.5 V |     | 6.0 | 500             | ns   |

|                                              |                  | V <sub>CC</sub> = 6.0 V |     | 6.0 | 400             | ns   |

| Ambient Operating Temperature                | T <sub>OPR</sub> |                         | -40 |     | +125            | °C   |

## QUICK REFERENCE DATA (GND = 5V; T = 25 °C)

| PARAMETER                                 | SYMBOL          | TEST CONDITIONS                                  | MIN | TYP | MAX | UNIT |

|-------------------------------------------|-----------------|--------------------------------------------------|-----|-----|-----|------|

| VCO Centre Frequency                      | f <sub>o</sub>  | C1=40pF; R1=3k $\Omega$ ;<br>V <sub>CC</sub> =5V |     | 19  |     | MHz  |

| Input Capacitance (Pin 5)                 | C <sub>IN</sub> |                                                  |     | 3.5 |     | pF   |

| Power Dissipation Capacitance per Package | C <sub>PD</sub> | (Note)                                           |     | 24  |     | pF   |

Note :  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ):

$$\boldsymbol{P}_{\!\scriptscriptstyle D} = \boldsymbol{C}_{\scriptscriptstyle PD} \times \boldsymbol{V_{\scriptscriptstyle CC}}^2 \times \boldsymbol{f}_{\!\scriptscriptstyle i} + \sum \left(\boldsymbol{C}_{\scriptscriptstyle L} \times \boldsymbol{V_{\scriptscriptstyle CC}}^2 \times \boldsymbol{f}_{\!\scriptscriptstyle O}\right)$$

where:  $f_i$  = input frequency in MHz;

C<sub>L</sub> = output load capacitance in pF;

$V_{CC}$  = supply voltage in V;

$f_o$  =output frequency in MHz;  $\sum (C_L \times V_{cc}^2 \times f_o)$  = sum of outputs.

# ■ DC CHARACTERISTICS (T<sub>A</sub> =25°C , unless otherwise specified)

Quiescent Supply Current (Voltages are referenced to GND (ground = 0 V))

| PARAMETER                               | SYMBOL | TEST CONDITIONS       |                                                                                             | MIN | TYP | MAX | UNIT |

|-----------------------------------------|--------|-----------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Quiescent Supply Current (VCO Disabled) | Icc    | V <sub>CC</sub> =6.0V | Pins 3, 5 and 14 at $V_{CC}$ ;<br>Pin 9 at GND; $I_{IN}$ at pins<br>3 and 14 to be excluded |     |     | 8.0 | μА   |

**Phase Comparator Section**

| Phase Comparator Section  PARAMETER                                  | SYMBOL                                  | TES                                                                                             | T CONDITIONS                             | MIN  | TYP  | MAX           | UNIT                  |  |   |     |

|----------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------|------|------|---------------|-----------------------|--|---|-----|

| DC Coupled                                                           | 51111B0L                                | V <sub>CC</sub> =2.0V                                                                           |                                          | 1.5  | 1.2  | .,,,,,,       | 3                     |  |   |     |

| (HIGH Level Input Voltage SIG <sub>IN</sub> ,                        | VIH                                     | V <sub>CC</sub> =4.5V                                                                           |                                          | 3.15 | 2.4  |               | V                     |  |   |     |

| COMP <sub>IN</sub> )                                                 |                                         | V <sub>CC</sub> =6.0V                                                                           |                                          | 4.2  | 3.2  |               |                       |  |   |     |

| DC Coupled                                                           |                                         | V <sub>CC</sub> =2.0V                                                                           |                                          |      | 0.8  | 0.5           |                       |  |   |     |

| (LOW Level Input Voltage SIG <sub>IN</sub> ,                         | $V_{IL}$                                | V <sub>CC</sub> =4.5V                                                                           |                                          |      | 2.1  | 1.35          | V                     |  |   |     |

| COMP <sub>IN</sub> )                                                 |                                         | V <sub>CC</sub> =6.0V                                                                           |                                          |      | 2.8  | 1.8           |                       |  |   |     |

| LUCLI Level Outeut Veltere                                           |                                         |                                                                                                 | V <sub>CC</sub> =2.0V                    | 1.9  | 2.0  |               |                       |  |   |     |

| HIGH Level Output Voltage (PCP <sub>OUT</sub> , PC <sub>nOUT</sub> ) | $V_{OH}$                                | $V_I = V_{IH}$ or $V_{IL}$ ,<br>- $I_{OUT} = 20\mu A$                                           | V <sub>CC</sub> =4.5V                    | 4.4  | 4.5  |               | V                     |  |   |     |

| ·                                                                    |                                         | - 1007 – 20μΑ                                                                                   | V <sub>CC</sub> =6.0V                    | 5.9  | 6.0  |               |                       |  |   |     |

| HIGH Level Output Voltage                                            | $V_{OH}$                                | V <sub>I</sub> =V <sub>IH</sub> or V <sub>IL</sub>                                              | $V_{CC}$ =4.5 $V_{c}$ - $I_{c}$ = 4.0 mA | 3.98 | 4.32 |               | V                     |  |   |     |

| (PCP <sub>OUT</sub> , PC <sub>nOUT)</sub>                            | <b>V</b> OH                             | VI-VIH OI VIL,                                                                                  | $V_{CC}$ =6.0V ,- $I_{O}$ = 5.2 mA       | 5.48 | 5.81 |               | V                     |  |   |     |

| OW Level Output Voltage                                              |                                         | V <sub>I</sub> =V <sub>IH</sub> or V <sub>IL,</sub>                                             | V <sub>CC</sub> =2.0V                    |      | 0    | 0.1           | ]                     |  |   |     |

| (PCP <sub>OUT</sub> , PC <sub>nOUT</sub> )                           | V <sub>OL</sub>                         | $I_{OUT} = 20 \mu A$                                                                            | V <sub>CC</sub> =4.5V                    |      | 0    | 0.1           | V                     |  |   |     |

| (1 Of Out, 1 Onout)                                                  |                                         |                                                                                                 |                                          |      |      | - 1001 – 20µA | V <sub>CC</sub> =6.0V |  | 0 | 0.1 |

| LOW Level Output Voltage                                             | $V_{OL}$                                | V <sub>I</sub> =V <sub>IH</sub> or V <sub>IL</sub>                                              | $V_{CC}$ =4.5 $V$ , $I_{O}$ = 4.0 mA     |      | 0.15 | 0.26          | V                     |  |   |     |

| (PCP <sub>OUT</sub> , PC <sub>nOUT</sub> )                           |                                         | VI-VIH OI VIL,                                                                                  | $V_{CC}$ =6.0V , $I_{O}$ = 5.2 mA        |      | 0.16 | 0.26          | V                     |  |   |     |

|                                                                      |                                         |                                                                                                 | V <sub>CC</sub> =2.0V                    |      |      | 3.0           |                       |  |   |     |

| Input Leakage Current                                                | ±l <sub>IN</sub>                        | $V_I = V_{CC}$ or                                                                               | V <sub>CC</sub> =3.0V                    |      |      | 7.0           | μA                    |  |   |     |

| (SIG <sub>IN</sub> , COMP <sub>IN</sub> )                            | ΞΊΝ                                     | GND                                                                                             | V <sub>CC</sub> =4.5V                    |      |      | 18.0          | μΑ                    |  |   |     |

|                                                                      |                                         |                                                                                                 | V <sub>CC</sub> =6.0V                    |      |      | 30.0          |                       |  |   |     |

| 3-State (OFF-state current PC2 <sub>OUT</sub> )                      | ±l <sub>OZ</sub>                        | V <sub>OUT</sub> = V <sub>CC</sub> or GND, V <sub>I</sub> =V <sub>IH</sub> or V <sub>IL</sub> , |                                          |      |      | 0.5           | μA                    |  |   |     |

| 3-State (STT -State Current T C2001)                                 | 5-State (OFF-State Current PGZOUT) ±102 |                                                                                                 | V <sub>CC</sub> =6.0V                    |      |      | 0.0           | μΑ                    |  |   |     |

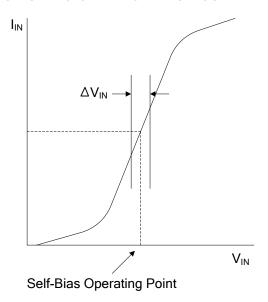

|                                                                      | R <sub>IN</sub>                         |                                                                                                 | <sub>IN</sub> at self-bias operating     |      | 800  |               | kΩ                    |  |   |     |

| Input Resistance (SIG <sub>IN</sub> , COMP <sub>IN</sub> )           |                                         |                                                                                                 | point; $\Delta V_I = 0.5V$ ;             |      | 250  |               | kΩ                    |  |   |     |

|                                                                      |                                         | V <sub>CC</sub> =6.0V (Fig. 7)                                                                  |                                          |      | 150  |               | kΩ                    |  |   |     |

**VCO Section** (Voltages are Referenced to GND (Ground = 0 V))

| PARAMETER                                                  | SYMBOL           | TES                                                                | ST CONDITIONS                                     | MIN    | TYP  | MAX  | UNIT |

|------------------------------------------------------------|------------------|--------------------------------------------------------------------|---------------------------------------------------|--------|------|------|------|

|                                                            |                  | V <sub>CC</sub> =3.0V                                              |                                                   | 2.1    | 1.7  |      |      |

| HIGH Level Input Voltage INH                               | F                | V <sub>CC</sub> =4.5V                                              |                                                   | 3.15   | 2.4  |      | V    |

|                                                            |                  | V <sub>CC</sub> =6.0V                                              |                                                   | 4.2    | 3.2  |      |      |

|                                                            |                  | V <sub>CC</sub> =3.0V                                              |                                                   |        | 1.3  | 0.9  |      |

| LOW Level Input Voltage INH                                | $V_{IL}$         | V <sub>CC</sub> =4.5V                                              |                                                   |        | 2.1  | 1.35 | V    |

|                                                            |                  | V <sub>CC</sub> =6.0V                                              |                                                   |        | 2.8  | 1.8  |      |

|                                                            |                  | \/-\/ or\/                                                         | V <sub>CC</sub> =3.0V                             | 2.9    | 3.0  |      |      |

| HIGH Level Output Voltage VCO <sub>OUT</sub>               | V <sub>OH</sub>  | $V_I = V_{IH}$ or $V_{IL}$ ,<br>- $I_{OUT} = 20 \mu A$             | V <sub>CC</sub> =4.5V                             | 4.4    | 4.5  |      | V    |

|                                                            |                  | - 1001 – 20μΑ                                                      | V <sub>CC</sub> =6.0V                             | 5.9    | 6.0  |      |      |

| HIGH Level Output Voltage VCO <sub>OUT</sub>               | $V_{OH}$         | V <sub>OH</sub> V <sub>I</sub> =V <sub>IH</sub> or V <sub>IL</sub> | $V_{CC}$ =4.5 $V$ , $-I_{OUT}$ = 4.0 mA           | 3.98   | 4.32 |      | v    |

| Trigit Level Output Voltage VCO <sub>00</sub> T            | VOH              | VI-VIH OI VIL                                                      | V <sub>CC</sub> =6.0V, -l <sub>OUT</sub> = 5.2 mA | 5.48   | 5.81 |      | V    |

|                                                            |                  | \/-\/ or\/                                                         | V <sub>CC</sub> =3.0V                             | n      | 0    | 0.1  |      |

| LOW Level Output Voltage VCO <sub>OUT</sub>                | $V_{OL}$         | $V_I = V_{IH}$ or $V_{IL}$ ,<br>$I_{OUT} = 20\mu A$                | V <sub>CC</sub> =4.5V                             | ).<br> | 0    | 0.1  | V    |

|                                                            |                  | 1001 - 20µA                                                        | V <sub>CC</sub> =6.0V                             |        | 0    | 0.1  |      |

| LOW Lovel Output Voltage VCO                               | \/               | V <sub>I</sub> =V <sub>IH</sub> or V <sub>ID</sub>                 | $V_{CC}$ =4.5V, $I_{OUT}$ = 4.0 mA                |        | 0.15 | 0.26 | V    |

| LOW Level Output Voltage VCO <sub>OUT</sub>                | V <sub>OL</sub>  | AI-AIH OL AIE                                                      | $V_{CC}$ =6.0V, $I_{OUT}$ = 5.2 mA                |        | 0.16 | 0.26 | V    |

| LOW Lovel Output Voltage C1. C1-                           | V                | 12/4 Or/4                                                          | $V_{CC}$ =4.5V, $I_{OUT}$ = 4.0 mA                |        |      | 0.4  | V    |

| LOW Level Output Voltage C1 <sub>A</sub> , C1 <sub>B</sub> | $V_{OL}$         | Vi=Viн or Vi∟                                                      | $V_{CC}$ =6.0V, $I_{OUT}$ =5.2 mA                 |        |      | 0.4  | V    |

| Input Leakage Current(INH, VCO <sub>IN</sub> )             | ±l <sub>IN</sub> | Vcc=6.0V, V                                                        | <sub>I</sub> =V <sub>CC</sub> or GND              |        |      | 0.1  | μΑ   |

# DC CHARACTERISTICS(Cont.)

# **VCO Section (Cont.)**

| PARAMETER                                    | SYMBOL      | TES                   | ST CONDITIONS         | MIN | TYP | MAX | UNIT |

|----------------------------------------------|-------------|-----------------------|-----------------------|-----|-----|-----|------|

|                                              |             | $V_{CC}$ =3.0 $V$     |                       | 3.0 |     | 300 |      |

| Resistance Range                             | R1          | V <sub>CC</sub> =4.5V |                       | 3.0 |     | 300 | kΩ   |

|                                              |             | V <sub>CC</sub> =6.0V |                       | 3.0 |     | 300 |      |

|                                              |             | $V_{CC}$ =3.0 $V$     |                       | 3.0 |     | 300 |      |

|                                              | ŀ           | V <sub>CC</sub> =4.5V | (Note)                | 3.0 |     | 300 | kΩ   |

|                                              |             | V <sub>CC</sub> =6.0V |                       | 3.0 |     | 300 |      |

|                                              |             | $V_{CC}$ =3.0 $V$     |                       | 40  |     |     |      |

| Capacitor Range                              | C1          | V <sub>CC</sub> =4.5V |                       | 40  |     |     | pF   |

|                                              |             | V <sub>CC</sub> =6.0V |                       | 40  |     |     |      |

|                                              |             | $V_{CC}$ =3.0 $V$     | Over the range        | 1.1 |     | 1.9 |      |

| Operating Voltage Range at VCO <sub>IN</sub> | $V_{VCOIN}$ | V <sub>CC</sub> =4.5V | specified for R1;     | 1.1 |     | 3.4 | V    |

|                                              | ļ           | V <sub>CC</sub> =6.0V | for linearity (Fig10) | 1.1 |     | 4.9 |      |

Note: The parallel value of R1 and R2 should be more than 2.7 k $\Omega$ . Optimum performance is achieved when R1 and/ or R2 are/is > 10 k $\Omega$ .

**Demodulator Section** (Voltages are Referenced to GND (Ground = 0 V))

| Demodulator Section (Voltages are Neiereneed to GND (Ground = 0 V)) |           |                       |                                  |     |     |     |      |  |  |  |

|---------------------------------------------------------------------|-----------|-----------------------|----------------------------------|-----|-----|-----|------|--|--|--|

| PARAMETER                                                           | SYMBOL    | TE                    | ST CONDITIONS                    | MIN | TYP | MAX | UNIT |  |  |  |

|                                                                     | $R_S$     | V <sub>CC</sub> =3.0V | At $R_S > 300 \text{ k}\Omega$   | 50  |     | 300 |      |  |  |  |

| Resistor Range                                                      |           | V <sub>CC</sub> =4.5V | the leakage current can          | 50  |     | 300 | kΩ   |  |  |  |

|                                                                     |           | V <sub>CC</sub> =6.0V | influence V <sub>DEMOUT</sub>    | 50  |     | 300 |      |  |  |  |

|                                                                     | $V_{OFF}$ | V <sub>CC</sub> =3.0V | $V_1 = V_{VCOIN} = 1/2 V_{CC};$  |     | ±30 |     |      |  |  |  |

| Offset Voltage VCO <sub>IN</sub> to V <sub>DEMOUT</sub>             |           | V <sub>CC</sub> =4.5V | values taken over R <sub>S</sub> |     | ±20 |     | mV   |  |  |  |

|                                                                     |           | V <sub>CC</sub> =6.0V | range                            |     | ±10 |     |      |  |  |  |

| Dunamia Outrut Basistanas at                                        |           | V <sub>CC</sub> =3.0V |                                  |     | 25  |     |      |  |  |  |

| Dynamic Output Resistance at                                        | $R_D$     | V <sub>CC</sub> =4.5V | $V_{DEMOUT} = 1/2 V_{CC}$        |     | 25  |     | Ω    |  |  |  |

| DEM <sub>OUT</sub>                                                  | ı         | V <sub>CC</sub> =6.0V |                                  |     | 25  |     |      |  |  |  |

# ■ AC CHARACTERISTICS (T<sub>A</sub> =25°C, unless otherwise specified)

**Phase Comparator Section** (GND = 0 V;  $t_R = t_F = 6$ ns;  $C_L = 50$ pF)

| PARAMETER                                                                         | SYMBOL                              | TEST COND             | DITIONS               | MIN | TYP | MAX | UNIT |

|-----------------------------------------------------------------------------------|-------------------------------------|-----------------------|-----------------------|-----|-----|-----|------|

| Brancastian Balay SIC                                                             |                                     | V <sub>CC</sub> =2.0V |                       |     | 63  | 200 |      |

| Propagation Delay SIG <sub>IN</sub> ,<br>COMP <sub>IN</sub> to PC1 <sub>OUT</sub> | t <sub>PHL</sub> / t <sub>PLH</sub> | V <sub>CC</sub> =4.5V | Fig.8                 |     | 23  | 40  | ns   |

| COMFIN to FC 100T                                                                 |                                     | V <sub>CC</sub> =6.0V |                       |     | 18  | 34  |      |

| Propagation Daloy SIC                                                             |                                     | V <sub>CC</sub> =2.0V |                       |     | 96  | 340 |      |

| Propagation Delay SIG <sub>IN</sub> , COMP <sub>IN</sub> to PCP <sub>OUT</sub>    | t <sub>PHL</sub> / t <sub>PLH</sub> | V <sub>CC</sub> =4.5V | Fig.8                 |     | 35  | 68  | ns   |

| COMI IN TO LOU                                                                    |                                     | V <sub>CC</sub> =6.0V |                       |     | 28  | 58  |      |

| Propagation Dolay SIC                                                             |                                     | V <sub>CC</sub> =2.0V |                       |     | 77  | 270 | ns   |

| Propagation Delay SIG <sub>IN</sub> ,<br>COMP <sub>IN</sub> to PC3 <sub>OUT</sub> | t <sub>PHL</sub> / t <sub>PLH</sub> | V <sub>CC</sub> =4.5V | Fig.8                 |     | 28  | 54  |      |

|                                                                                   |                                     | V <sub>CC</sub> =6.0V |                       |     | 22  | 46  |      |

| 3-State Output Enable Time                                                        |                                     | V <sub>CC</sub> =2.0V | Fig.9                 |     | 83  | 280 | ns   |

| SIG <sub>IN</sub> , COMP <sub>IN</sub> to PC2 <sub>OUT</sub>                      | t <sub>PZH</sub> / t <sub>PZL</sub> | V <sub>CC</sub> =4.5V |                       |     | 30  | 56  |      |

| GIGIN, COIVII IN 10 1 G2001                                                       |                                     | V <sub>CC</sub> =6.0V |                       |     | 24  | 48  |      |

| 3-State Output Disable Time                                                       |                                     | V <sub>CC</sub> =2.0V | Fig.9                 |     | 99  | 325 | ns   |

| SIG <sub>IN</sub> , COMP <sub>IN</sub> to PC2 <sub>OUT</sub>                      | t <sub>PHZ</sub> / t <sub>PLZ</sub> | V <sub>CC</sub> =4.5V |                       |     | 36  | 65  |      |

| SIGIN, COIVII IN 10 1 C2001                                                       |                                     | V <sub>CC</sub> =6.0V |                       |     | 29  | 55  |      |

|                                                                                   |                                     | V <sub>CC</sub> =2.0V |                       |     | 19  | 75  |      |

| Output Transition Time                                                            | t <sub>PHZ</sub> / t <sub>PLZ</sub> | V <sub>CC</sub> =4.5V | Fig.8                 |     | 7   | 15  | ns   |

|                                                                                   |                                     | V <sub>CC</sub> =6.0V |                       |     | 6   | 13  | 1    |

| AC Coupled Input Consitivity                                                      |                                     | V <sub>CC</sub> =2.0V | f <sub>i</sub> = 1MHz |     | 9   |     |      |

| AC Coupled Input Sensitivity                                                      | V                                   | V <sub>CC</sub> =3.0V |                       |     | 11  |     | mV   |

| (Peak-To-Peak Value)<br>at SIG <sub>IN</sub> or COMP <sub>IN</sub>                | $V_{IN(P-P)}$                       | V <sub>CC</sub> =4.5V |                       |     | 15  |     |      |

| at Sign of Solvii IN                                                              |                                     | V <sub>CC</sub> =6.0V |                       |     | 33  |     |      |

# **VCO Section** (GND = 0 V; $t_R = t_F = 6$ ns; $C_L = 50$ pF)

| PARAMETER                                   | SYMBOL                | TES                   | ST CONDITIONS                                | MIN  | TYP  | MAX | UNIT |

|---------------------------------------------|-----------------------|-----------------------|----------------------------------------------|------|------|-----|------|

| Fraguency Stability with                    |                       | V <sub>CC</sub> =3.0V | $V_{IN} = V_{VCOIN} = 1/2 V_{CC};$           |      | 0.2  |     |      |

| Frequency Stability with Temperature Change | Δf/T                  | V <sub>CC</sub> =4.5V | R1 = 100 kΩ; R2 = ∞;                         |      | 0.15 |     | %/K  |

| Temperature Change                          |                       | V <sub>CC</sub> =6.0V | C1= 100 pF                                   |      | 0.14 |     |      |

| VCO Centre Frequency<br>(duty Factor = 50%) |                       | V <sub>CC</sub> =3.0V | $V_{VCOIN} = 1/2 V_{CC};$                    | 7.0  | 10.0 |     |      |

|                                             | f <sub>o</sub>        | V <sub>CC</sub> =4.5V | R1 = 3 kΩ;R2 = ∞;                            | 11.0 | 17.0 |     | MHz  |

| (duty Factor = 30 %)                        |                       | V <sub>CC</sub> =6.0V | C1 = 40 pF                                   | 13.0 | 21.0 |     |      |

|                                             |                       | V <sub>CC</sub> =3.0V | R1 = 100 kΩ; R2 = ∞;<br>C1 = 100 pF;(Fig.10) |      | 1.0  |     | %    |

| VCO Frequency Linearity                     | $\Delta f_{VCO}$      | V <sub>CC</sub> =4.5V |                                              |      | 0.4  |     |      |

|                                             |                       | V <sub>CC</sub> =6.0V |                                              |      | 0.3  |     |      |

|                                             |                       | V <sub>CC</sub> =3.0V |                                              |      | 50   |     |      |

| Duty Factor at VCO <sub>OUT</sub>           | $\delta_{\text{VCO}}$ | V <sub>CC</sub> =4.5V |                                              |      | 50   |     | %    |

|                                             |                       | V <sub>CC</sub> =6.0V |                                              |      | 50   |     |      |

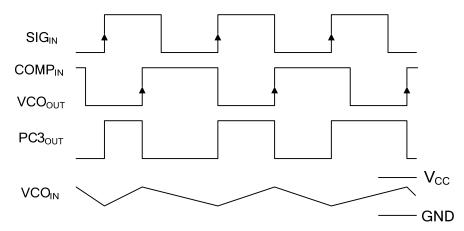

## ■ PHASE COMPARATORS

If the signal swing is between the standard HC family input logic levels, the signal input (SIG<sub>IN</sub>) can be directly coupled to the self-biasing amplifier at pin 14. Capacitive coupling is required for signals with smaller swings.

#### Phase comparator 1 (PC1)

This is an EXCLUSIVE-OR network. To obtain the maximum locking range, the signal and comparator input frequencies  $(f_i)$  must have a 50% duty factor.

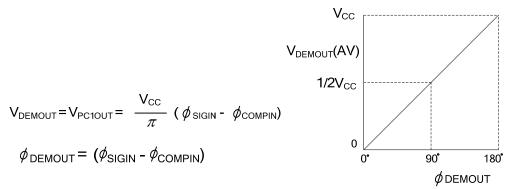

The transfer characteristic of PC1, assuming ripple ( $f_r = 2f_i$ ) is suppressed, is:

$$V_{\text{DEMOUT}} = \frac{V_{\text{cc}}}{\pi} (\phi_{\text{SIGIN}} - \phi_{\text{COMPIN}})$$

Where  $V_{DEMOUT}$  is the demodulator output at pin 10;  $V_{DEMOUT} = V_{PC1OUT}$  (via low-pass filter).

The phase comparator gain is:

$$K_P = \frac{V_{cc}}{\pi} (V/r)$$

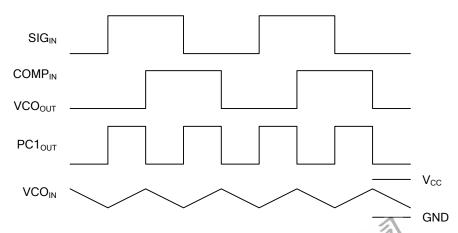

As shown in Fig.1, the average output voltage from PC1, fed to the VCO input via the low-pass filter and seen at the demodulator output at pin 10 ( $V_{DEMOUT}$ ) is the resultant of the phase differences of signals ( $SIG_{IN}$ ) and the comparator input ( $COMP_{IN}$ ). The average of  $V_{DEMOUT}$  is equal to  $V_{CC}/2$  when there is no signal or noise at  $SIG_{IN}$  and with this input the VCO oscillates at the centre frequency ( $f_O$ ). As shown in Fig.2 it is the typical waveforms for the PC1 loop locked at  $f_O$ .

Fig.1 Phase comparator 1: average output voltage versus input phase difference.

Fig.2 Typical waveforms for PLL using phase comparator 1, loop locked at fo.

The frequency capture range  $(2f_c)$  is he frequency range of input signals on which the PLL will lock if it was initially out-of-lock. The frequency lock range  $(2f_L)$  is the frequency range of input signals on which the loop will stay locked if it was initially in lock. The capture range is smaller or equal to the lock range.

With PC1, the low-pass filter characteristics determine the capture range which can be made as large as the lock range.

This configuration retains lock even with very noisy input signals. Typical behavior of this type of phase comparator is that it can lock to input frequencies close to the harmonics of the VCO centre frequency.

# PHASE COMPARATORS (Cont.)

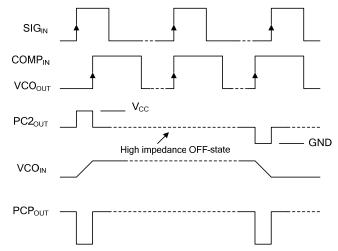

#### Phase comparator 2 (PC2)

This is a positive edge-triggered phase and frequency detector. If the PLL is using the comparator, the loop is controlled by positive signal transitions and the duty factors of SIG<sub>IN</sub> and COMP<sub>IN</sub> are not important. PC2 is comprised of two D-type flip-flops, control-gating and a 3-state output stage. The circuit function is as an up-down counter (Logic Diagram) for SIG<sub>IN</sub> causes an up-count and COMP<sub>IN</sub> causes a down-count.

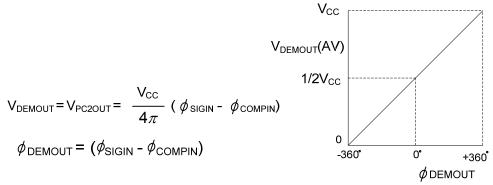

The transfer function of PC2, assuming ripple  $(f_r = f_i)$  is suppressed, is

$$V_{\text{DEMOUT}} = \frac{V_{\text{cc}}}{4\pi} (\phi_{\text{SIGIN}} - \phi_{\text{COMPIN}})$$

$V_{\text{DEMOUT}} = \frac{V_{\text{cc}}}{4\pi} (\phi_{\text{SIGIN}} - \phi_{\text{COMPIN}})$  where  $V_{\text{DEMOUT}}$  is the demodulator output at pin 10;  $V_{\text{DEMOUT}} = V_{\text{PC2OUT}}$  (via low-pass filter).

The phase comparator gain is:

$$K_p = \frac{V_{cc}}{4\pi} (V/r)$$

As shown in Fig.3,  $V_{\text{DEMOUT}}$  is the resultant of the initial phase differences of  $SIG_{IN}$  and  $COMP_{IN}$ . Typical waveforms for the PC2 loop locked at fo are shown in Fig.4.

Fig.3 Phase comparator 2: average output voltage versus input phase difference.

Fig.4 Typical waveforms for PLL using phase comparator 2, loop locked at fo.

If the frequencies of SIG<sub>IN</sub> and COMP<sub>IN</sub>, are equal but the phase of SIG<sub>IN</sub> leads that of COMP<sub>IN</sub>, the p-type output driver at PC2<sub>OUT</sub> is held "ON" for a time corresponding to the phase difference ( $\phi_{DEMOUT}$ ). If the phase of SIG<sub>IN</sub> lags that of COMP<sub>IN</sub>, the n-type driver is held "ON".

If the frequency of SIG<sub>IN</sub> is higher than that of COMP<sub>IN</sub>, the p-type output driver is held "ON" for most of the input signal cycle time, and for the remainder of the cycle both n and p-type drivers are "OFF" (3-state). If the frequency of SIG<sub>IN</sub> is lower than that of COMP<sub>IN</sub>, the n-type driver that is held "ON" for most of the cycle. Then the voltage at the capacitor (C2) of the low-pass filter connected to PC2<sub>OUT</sub> varies until the signal and comparator inputs are equal in both phase and frequency. At this stable state the voltage on C2 remains constant as the PC2 output is in 3-state and the VCO input at pin 9 is a high impedance. Also in the condition, the signal at the phase comparator

pulse output (PCP<sub>OUT</sub>) is a HIGH level, and it indicates a locked condition.

For PC2, there is no phase difference between SIG<sub>IN</sub> and COMP<sub>IN</sub> over the full frequency range of the VCO. And as the low-pass filter, the power dissipation is reduced because both p and n-type drivers are "OFF" for most of the signal input cycle. It should be noted that the PLL lock range for this type of phase comparator is equal to the capture range and this is independent of the low-pass filter. The VCO adjusts to its lowest frequency via PC2 when no signal present at SIG<sub>IN</sub>.

# PHASE COMPARATORS (Cont.)

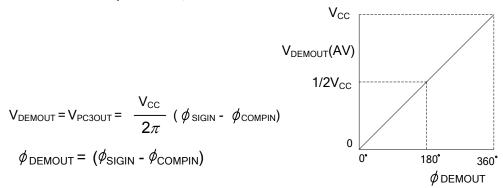

#### Phase comparator 3 (PC3)

This is a positive edge-triggered sequential phase detector using an RS-type flip-flop. If this comparator is used, the loop is controlled by positive signal transitions and the duty factors of SIG<sub>IN</sub> and COMP<sub>IN</sub> are not important. The transfer characteristic of PC3, assuming ripple  $(f_r = f_i)$  is suppressed, is:

$$V_{\text{DEMOUT}} = \frac{V_{\text{cc}}}{2\pi} (\phi_{\text{SIGIN}} - \phi_{\text{COMPIN}})$$

where  $V_{DEMOUT} = V_{PC3OUT}$  (via low-pass filter).

The phase comparator gain is:

$$K_P = \frac{V_{cc}}{2\pi} (V/r)$$

As shown in Fig.5, the average output voltage from PC3, fed to the low-pass filter and seen at the demodulator output at pin 10 (V<sub>DEMOUT</sub>), is the resultant of the phase differences of SIG<sub>IN</sub> and COMP<sub>IN</sub>. As shown in Fig.6, it is the typical waveforms for the PC3 loop locked at fo.

Fig.5 Phase comparator 3: average output voltage versus input phase difference.

Fig.6 Typical waveforms for PLL using phase comparator 3, loop locked at fo.

The phase-to-output response characteristic of PC3 (Fig.5) differs from that of PC2, as the phase angle between SIG<sub>IN</sub> and COMP<sub>IN</sub> varies between 0° and 360° and 180° is the centre frequency. And the voltage swing of PC3 is greater than that of PC2 for input phase differences, but as a consequence the tipple content of VCO input phase consignal pre signal is higher. Both of the PLL lock range and capture range of this type of phase comparator are dependent on the low-pass filter. The VCO adjusts to its lowest frequency via PC3, when no signal present at SIG<sub>IN</sub>.

# FIGURE REFERENCES FOR DC CHARACTERISTICS

Fig.7 Typical input resistance curve at SIG<sub>IN</sub>, COMP<sub>IN</sub>.

UNISONIC TECHNOLOGIES CO., LTD www.unisonic.com.tw

# ■ AC WAVEFORMS

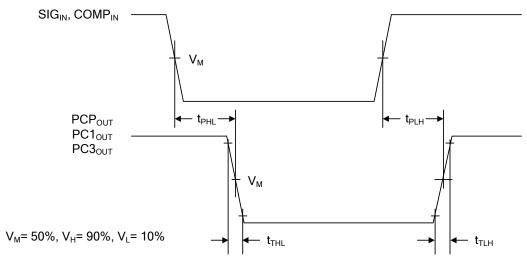

Fig.8 Waveforms showing input (SIG<sub>IN</sub>, COMP<sub>IN</sub>) to output (PCP<sub>OUT</sub>, PC1<sub>OUT</sub>, PC3<sub>OUT</sub>) propagation delays and the output transition times.

$V_M = 50\%, V_H = 90\%, V_L = 10\%$

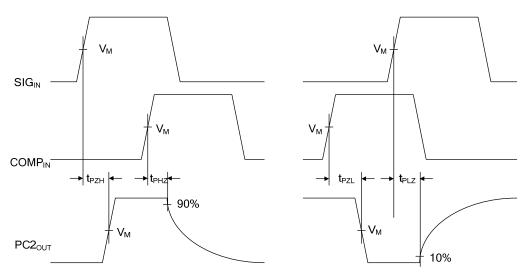

Fig.9 Waveforms showing the 3-state enable and disable times for  $PC2_{OUT}$ .

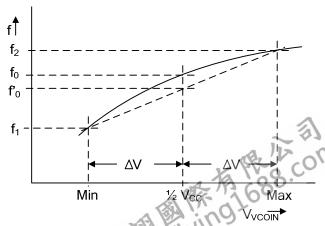

Fig.10 Definition of VCO frequency linearity:  $\Delta V = 0.5 \text{ V}$  over the  $V_{CC}$  range: For VCO linearity  $f'_0 = (f_1 + f_2)/2$ , linearity  $(f'_0 - f_0)/f'_0 \times 100\%$

## ■ APPLICATION INFORMATION

This is a reference for the values of external components to be used with the **U74HC4046A** in a PLL system. The ranges of the values of the components:

| Component | Value                   |  |

|-----------|-------------------------|--|

| R1        | 3 kΩ ~ 300 kΩ           |  |

| R2        | 3 kΩ ~ 300 kΩ           |  |

| R1+R2     | Parallel value > 2.7 kΩ |  |

| C1        | Greater than 40 pF      |  |

# VCO Frequency Without Extra Offset (Phase comparator: PC1, PC2 or PC3)

Frequency Characteristic:

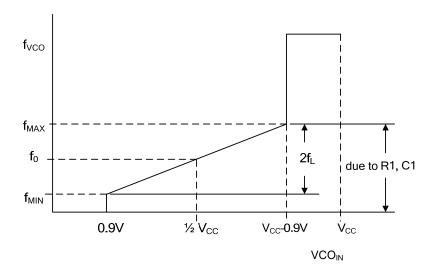

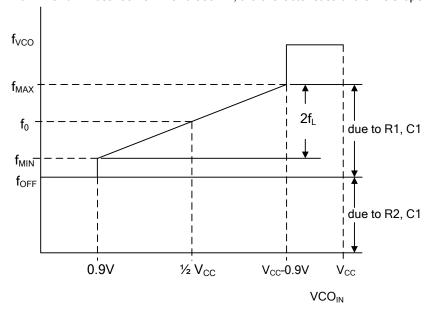

With R2 =  $\infty$  and R1 between 3 k $\Omega$  and 300 k $\Omega$ , the characteristics of the VCO operation will be as shown in Fig.11 (Due to R1, C1 time constant a small offset remains when R2 =  $\infty$ ).

Fig.11 Frequency characteristic of VCO operating without offset:  $f_0$  = centre frequency;  $2f_L$  = frequency lock range.

# ■ APPLICATION INFORMATION (Cont.)

VCO Frequency with Extra Offset (Phase Comparator: PC1, PC2 or PC3)

Frequency characteristic:

With R1 and R2 between 3 k $\Omega$  and 300 k $\Omega$ , the characteristics of the VCO operation will be as shown in Fig.12.

Fig.12 Frequency characteristic of VCO operating with offset:

$f_0$  = centre frequency;  $2f_L$  = frequency lock range.

PC1, PC2 or PC3

Selection of R1, R2 and C1

Given  $f_o$  and  $f_L,$  determine the value of R1  $\!\times$  C1

Calculate  $f_{OFF}$  from the equation  $f_{OFF} = f_O - 1.6f_L$

Obtain the values of C1 and R2

Calculate the value of R1 from the value of C1 and R1×C1.

| Subject                                                      | Phase comparator | Design considerations                                                                         |

|--------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------|

| PLL Conditions with no Signal at the SIG <sub>IN</sub> Input | PC1              | VCO adjusts to $f_0$ with $\phi_{DEMOUT} = 90^{\circ}$ and $V_{VCONIN} = 1/2 V_{CC}$ (Fig.1). |

|                                                              | PC2              | VCO adjusts to $f_0$ with $\phi_{DEMOUT}$ = -360° and $V_{VCONIN}$ = min. (Fig.3).            |

|                                                              | PC3              | VCO adjusts to $f_o$ with $\phi_{DEMOUT}$ = -360° and $V_{VCONIN}$ = min. (Fig.5).            |

# ■ APPLICATION INFORMATION(Cont.)

PLL Frequency Capture Range (Phase comparator: PC1, PC2 or PC3)

Loop filter component selection

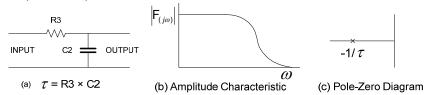

A small capture range (2f<sub>C</sub>) is obtained if  $2f_C \approx \frac{1}{\pi} \sqrt{2\pi f_L / \tau}$

Fig.13 Simple loop filter for PLL without offset; R3  $\geq$  500  $\Omega$ .

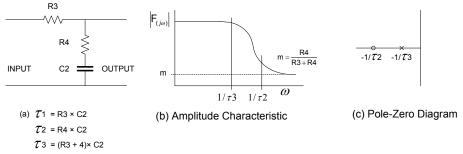

Fig.14 Simple loop filter for PLL with offset; R3 + R4  $\geq$  500  $\Omega$ .

| Subject                                    | Phase comparator | Design considerations                                               |

|--------------------------------------------|------------------|---------------------------------------------------------------------|

| DLL Locks on Harmonics at Centre Frequency | PC1 or PC3       | Yes                                                                 |

| PLL Locks on Harmonics at Centre Frequency | PC2              | No                                                                  |

| Naisa Daigation at Cignal Innut            | PC1              | High                                                                |

| Noise Rejection at Signal Input            | PC2 or PC3       | Low                                                                 |

|                                            | PC1              | $f_r = 2f_i$ , large ripple content at $\phi_{DEMOUT} = 90^\circ$   |

| AC Ripple Content when PLL is Locked       | PC2              | $f_r = f_i$ , small ripple content at $\phi_{DEMOUT} = 0^\circ$     |

|                                            | PC3              | $f_r = f_i$ , large ripple content at $\phi_{DEMOUT} = 180^{\circ}$ |

#### PLL DESIGN EXAMPLE

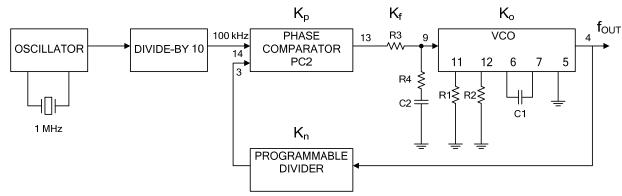

Fig.15 Frequency Synthesizer.

The parameters of the frequency synthesizer in Fig.15:

Output frequency: 2 MHz to 3 MHz

Frequency steps: 100kHz

Settling time: 1ms Overshoot: < 20%

The Open-Loop Gain is:  $H(s) \times G(s) = K_o \times K_f \times K_o \times K_n$

Where:  $K_p$  = phase comparator gain

K<sub>f</sub> = low-pass filter transfer gain

Ko = Kv/s VCO gain  $K_n = 1/n$  divider ratio

The programmable counter ratio  $K_n$  can be found as follows:

$$N_{\text{Min}} = \frac{f_{\text{out}}}{f_{\text{step}}} = \frac{2\text{MHz}}{100\text{kHz}} = 20$$

$$N_{\text{Max}} = \frac{f_{\text{out}}}{f_{\text{step}}} = \frac{3MHz}{100kHz} = 30$$

The VCO is set by the values of R1, R2 and C1, R2 =  $10 \text{ k}\Omega$  (adjustable). The values can be determined using the information in the section "DESIGN CONSIDERATIONS".

With  $f_0$  = 2.5MHz and  $f_L$  =500 kHz this gives the following values ( $V_{CC}$  = 5.0 V):

R1 =  $10 \text{ k}\Omega$ ; R2 =  $10 \text{ k}\Omega$ ; C1 = 500 pF

The VCO gain is:

$$K_V = \frac{2f_L \times 2 \times \pi}{0.9 - (V_{CC} - 0.9)} = \frac{1 MHz}{3.2} \times 2\pi \approx 2 \times 10^6 \, r \, / \, s \, / \, V$$

The gain of the phase comparator is:  $K_p = \frac{V_{CC}}{4\pi} = 0.4 \text{V/r}$

The transfer gain of the filter is given by:  $K_f = \frac{1 + \tau_2 S}{1 + (\tau_1 + \tau_2) S}$  Where:  $\tau_1 = R3C2$  and  $\tau_2 = R4C2$

The characteristics equation is:  $1 + H(S) \times G(S) = 0$

This results in:

$$S^2 + \frac{1 + K_p \times K_v \times K_n \times \tau_2}{(\tau_1 + \tau_2)} S + \frac{K_p \times K_v \times K_n}{(\tau_1 + \tau_2)} = 0$$

Damping Value  $\zeta$  is Defined as follows:  $\zeta = \frac{1}{2\omega_n} \times \frac{1 + K_p \times K_v \times K_n \times \tau_2}{(\tau_1 + \tau_2)}$ UNISONIC TECHNOLOGIES CO

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**CMOS IC**