U8C3525

**Preliminary**

# LINEAR INTEGRATED CIRCUIT

# 8 BIT SERIAL-IN PARALLEL-OUT VALVE DRIVER

#### **■** DESCRIPTION

The **U8C3525** is an 8-Bit Serial-In Parallel-Out driver with Error Detection to the solenoid valve drive. The device incorporates shift registers, data latches, and constant current circuitry on the silicon CMOS chip. The maximum output current value of one channel is Approximately limited to 250mA by Built-in constant current source.

The **U8C3525** has two power supplies,  $V_{DD}$  provides power to Internal control and communication modules. The range of  $V_{DD}$  is 5V to 18V.  $PV_{DD}$  is used to absorb the inductive coil reverse-phase current and the range of  $PV_{DD}$  is 5V to 35V.

Its built-in open/short detection circuits help users detect Load state of the detection channels. System retrieve the error messages to indicate which channel has failure by serial output data.

## **■ FEATURES**

\*V<sub>DD</sub> range: V<sub>DD</sub> 5V to18V

PV<sub>DD</sub> 5V to 35V

- \*Maximum clock frequency: 1MHz

- \*current limit of Each channel:250mA

- \*Built-in open/short detection

- \*Short protect

- \*Detecting response

- \*Internal reverse diode of PV<sub>DD</sub> to Absorb reverse current from coil

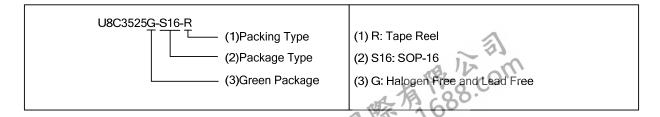

## ORDERING INFORMATION

| Ordering Number | Package | Packing   |

|-----------------|---------|-----------|

| U8C3525G-S16-R  | SOP-16  | Tape Reel |

www.unisonic.com.tw 1 of 6

## **MARKING**

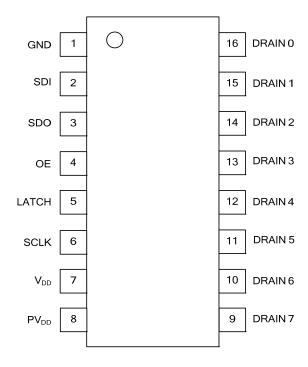

#### **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN NO.                                                                  | PIN NAME                                                                                                | DESCRIPTION                                                                                               |  |  |  |  |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                                                                        | GND                                                                                                     | Ground terminal                                                                                           |  |  |  |  |

| 2                                                                        | SDI                                                                                                     | Serial data input terminal.                                                                               |  |  |  |  |

| 3                                                                        | SDO                                                                                                     | Serial data output terminal.                                                                              |  |  |  |  |

| 4                                                                        | OE                                                                                                      | Output enable terminal: 'L' for all outputs are turned off, 'H' for all outputs are active.               |  |  |  |  |

| 5                                                                        | LATCH                                                                                                   | Input terminal of data strobe. Data on shift register goes through when 'H'.  Otherwise, data is latched. |  |  |  |  |

| 6                                                                        | SCLK                                                                                                    | Synchronous clock input terminal for serial data transfer. Data is sampled at the rising edge of SCLK.    |  |  |  |  |

| 7                                                                        | $V_{DD}$                                                                                                | Supply voltage terminal.                                                                                  |  |  |  |  |

| 8                                                                        | $PV_{DD}$                                                                                               | Power Supply voltage terminal. To absorb the inductive load reverse current of Driver-side                |  |  |  |  |

| 9-16                                                                     | Drian0 ~ Drain7                                                                                         | Sink constant-current outputs (open-drain).                                                               |  |  |  |  |

|                                                                          | 9-16 Drian0 ~ Drain7 Sink constant-current outputs (open-drain).  UNISONIC TECHNOLOGIES CO., LTD 2 of 6 |                                                                                                           |  |  |  |  |

| UNISONIC TECHNOLOGIES CO., LTD www.unisonic.com.tw  2 of 6 QW-R126-048.a |                                                                                                         |                                                                                                           |  |  |  |  |

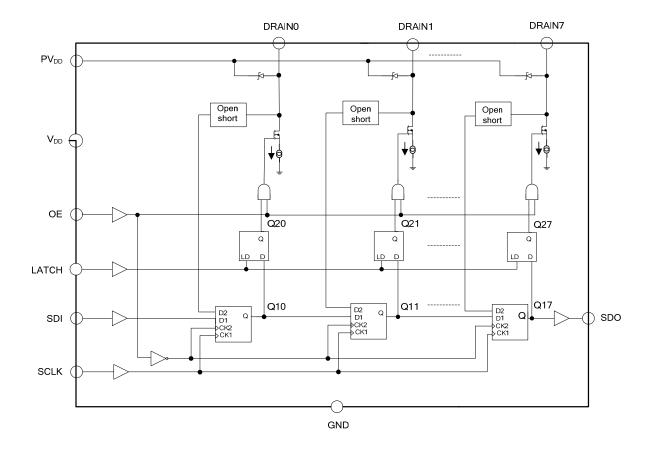

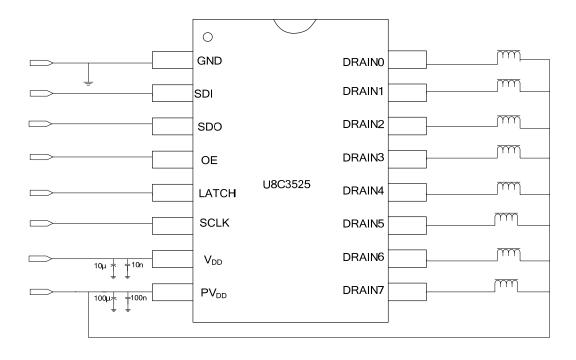

## **BLOCK DIAGRAM**

## ABSOLUTE MAXIMUM RATING

| PARAMETER                           | SYMBOL           | RATINGS                     | UNIT |

|-------------------------------------|------------------|-----------------------------|------|

| Voltage On Terminals                | $V_{DD}$         | -0.5 ~ 18                   | V    |

| Voltage On Terminals                | $V_{IN}$         | -0.5 ~ V <sub>CC</sub> +0.5 | V    |

| Power Dissipation (Temperature=25°) | $P_{D}$          | 1                           | W    |

| Operational Temperature Range       | $T_J$            | -30 ~ +70                   | °C   |

| Storage Temperature Range           | T <sub>STG</sub> | -40 ~ +150                  | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

## **■ RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                     | SYMBOL               | MIN | TYP | MAX | UNIT |

|-------------------------------|----------------------|-----|-----|-----|------|

| Power Supply                  | $V_{DD}$             | 5   | 12  | 18  | V    |

| Power Supply                  | $PV_{DD}$            | 5   |     | 35  | V    |

| Input Digital Clock Frequency | f <sub>SCLK</sub>    |     |     | 1   | MHz  |

| SCLK Pulse Width              | T <sub>SCLK</sub>    | 450 |     |     | ns   |

| LATCH Pulse Width             | T <sub>LATCH</sub>   | 450 |     |     | ns   |

| OE Pulse Width                | T <sub>OE</sub>      | 2   |     |     | us   |

| OE to SCLK Rise               | T <sub>OE-SCLK</sub> | 2   |     |     | us   |

# ■ TIMING SEQUENCE PARAMETER (T<sub>A</sub> =25°C, unless otherwise specified)

| PARAMETER                      | SYMBOL              | TEST CONDITIONS                     | MIN | TYP      | MAX | UNIT  |

|--------------------------------|---------------------|-------------------------------------|-----|----------|-----|-------|

| Supply Current                 | I <sub>ON</sub>     | PV <sub>DD</sub> =24V, Channel On   |     | 2.3      |     | mA    |

| Supply Current                 | I <sub>OFF</sub>    | PV <sub>DD</sub> =24V, Channel Off  |     | 1.9      |     | mA    |

| Output Voltage High (SDO)      | V <sub>OH</sub>     |                                     |     | $V_{DD}$ |     | V     |

| Input High Voltage             | V <sub>IH</sub>     |                                     | 3   |          | 18  | V     |

| Input Low Voltage              | $V_{IL}$            |                                     |     |          | 0.8 | V     |

| Limiting Current               | I <sub>LIMIT</sub>  |                                     | 250 |          |     | mA/ch |

| Output Voltage of Each Channel | V <sub>DS_ON</sub>  | Channel On, I <sub>OUT</sub> =150mA |     |          | 1   | V     |

| Maximum Power Voltage Supply   | V <sub>DS-OFF</sub> | Channel Off                         | 35  |          |     | V     |

# **TYPICAL APPLICATION CIRCUIT**

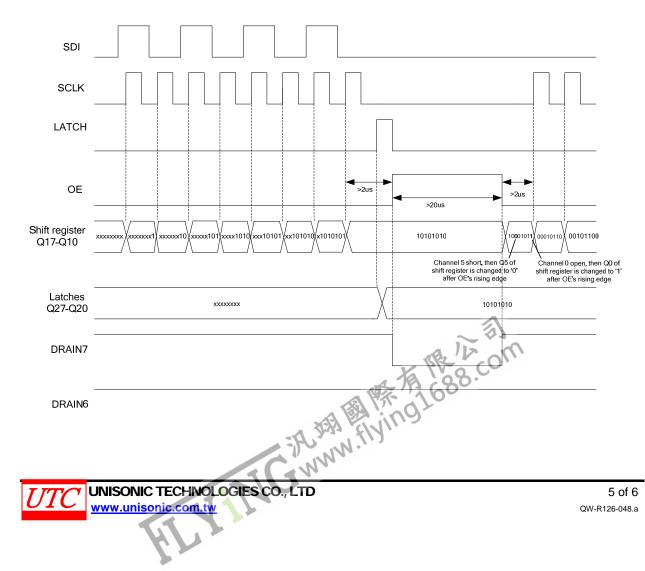

## **TIMING DIAGRAM**

#### ■ CIRCUIT DESCRIPTION

The **U8C3525** is an 8-Bit Serial-In Parallel-Out driver for Solenoid valve. The state of outputs Drain0 ~ Drain7 are controlled by the latch data Q20~Q27 and OE signal. When OE is high, if a channel corresponding data latch is 1, then the channel output is turned on, the switch from the output terminal to ground in the ON state.

**U8C3525**'s constant current technology make The maximum output current limited to around 250mA, which can effectively prevent the chip or peripheral devices from damaging caused by load short. If a channel corresponding data latch is 0, the output channel is switched off, in a high impedance state. When OE is low, no matter what the value of the latch data, the output channels are turned off. It can withstand high voltage above 35V when the outputs are turned off.

#### ■ OPEN/SHORT DETECTION

The result of open/short detection of U8C3525 could be retrieved from serial-out (DAO) data. Once the load of a channel in Open state or short state, the chip can be detected in time and quickly Shutdown the load shorted channel which the chip from can overheating and external load. The test results stored to the shift register when OE Falling edge .lt can be removed from SDO end of the serial at SCLK action reading back to the controller.

The controller will read back the data before sending out now Control data for comparison, if exactly the same, it means the load in good condition, no open short circuit, if a bit of data sent out is 1, 0 read back, it indicates that the corresponding channel bit data load short circuit occurs, if a bit of data to send out is 0, 1 read back, the table Shows the bit data corresponding to the channel occurred Open load.

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.