# **UCS1657S**

# LINEAR INTEGRATED CIRCUIT

# HIGH PERFORMANCE CURRENT MODE POWER SWITCH

#### DESCRIPTION

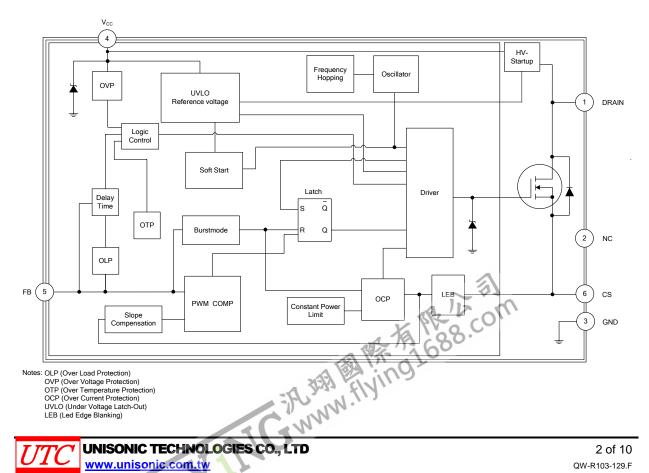

The UTC **UCS1657S** is an integrated PWM controller and Power MOSFET specifically designed for switching operation with minimal external components. The UTC **UCS1657S** is designed to provide several special enhancements to satisfy the needs, for example, Power-Saving mode for low standby power, Frequency Hopping, Constant Output Power Limiting, Slope Compensation ,Over Current Protection (OCP), Over Voltage Protection (OVP), Over Load Protection (OLP), Under Voltage Lock Out (UVLO), Over Temperature Protection (OTP), etc. IC will be shutdown or can auto-restart in situations.

#### **■ FEATURES**

- \* Internal Power MOSFET (650V)

- \* Programming Gate Driver Capability

- \* Frequency hopping for Improved EMI Performance.

- \* Lower than 30mW Standby Power Design

- \* Linearly decreasing frequency to 20~35KHz during light load

- \* Internal Soft start

- \* Internal Slope Compensation

- \* Constant Power Limiting for universal AC input Range

- \* Gate Output Maximum Voltage Clamp (16V)

- \* Over temperature protection

- \* Overload protection

- \* Over voltage protection

- \* Leading edge blanking

- \* Cycle-by-Cycle current limiting

- \* Under Voltage Lock Out

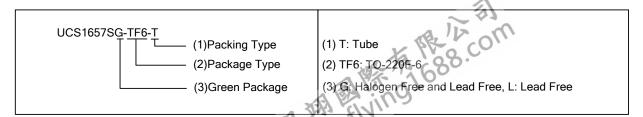

# **■ ORDERING INFORMATION**

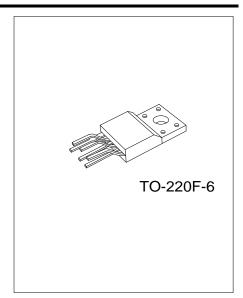

| Ordering Number |                 | Daaltana  | Doolsing |  |

|-----------------|-----------------|-----------|----------|--|

| Lead Free       | Halogen Free    | Package   | Packing  |  |

| UCS1657SL-TF6-T | UCS1657SG-TF6-T | TO-220F-6 | Tube     |  |

www.unisonic.com.tw 1 of 10

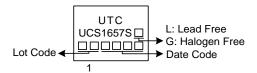

# **MARKING**

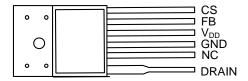

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTION**

| PIN NO. | PIN NAME | DESCRIPTION                                                                                              |

|---------|----------|----------------------------------------------------------------------------------------------------------|

| 1       | DRAIN    | Power MOSFET drain                                                                                       |

| 2       | NC       |                                                                                                          |

| 3       | GND      | Ground                                                                                                   |

| 4       | Vcc      | Supply voltage                                                                                           |

| 5       | FB       | Feedback input pin. The PWM duty cycle is determined by voltage level into this pin and SENSE pin input. |

| 6       | CS       | Current sense input pin. Connected to MOSFET current sensing resistor node.                              |

#### **BLOCK DIAGRAM**

# ■ **ABSOLUTE MAXIMUM RATING** (T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER               | SYMBOL           | RATINGS            | UNIT |

|-------------------------|------------------|--------------------|------|

| Supply Voltage          | V <sub>CC</sub>  | 33                 | V    |

| Input Voltage to FB Pin | $V_{FB}$         | -0.3 ~ 6.5         | V    |

| Input Voltage to CS Pin | V <sub>CS</sub>  | -0.3 ~ 6.5         | V    |

| Junction Temperature    | $T_J$            | +150               | °C   |

| Operating Temperature   | T <sub>OPR</sub> | -40 ~ +125         | °C   |

| Storage Temperature     | T <sub>STG</sub> | -50 ~ <b>+</b> 150 | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

# **■ OPERATING RANGE**

| PARAMETER                             | SYMBOL          | RATINGS | UNIT |

|---------------------------------------|-----------------|---------|------|

| Supply Voltage                        | V <sub>CC</sub> | 10 ~ 24 | V    |

| Open Frame Output Power for 85~264VAC | Po MAX          | 100     | W    |

# **■ ELECTRICAL CHARACTERISTICS**

| PARAMETER                                        | SYMBOL                | TEST CONDITIONS                            | MIN  | TYP  | MAX  | UNIT  |  |

|--------------------------------------------------|-----------------------|--------------------------------------------|------|------|------|-------|--|

| Supply Section                                   |                       |                                            |      |      |      | 51411 |  |

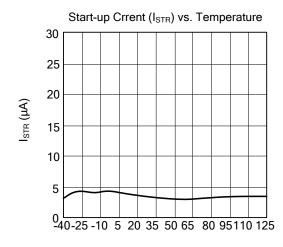

| Start Up Current                                 | I <sub>ST</sub>       | V <sub>CC</sub> =V <sub>THD (ON)</sub> -1V |      | 2    | 15   | μA    |  |

| Supply Current With Switch                       | I <sub>OP</sub>       | V <sub>FB</sub> =3.5V                      |      | 3.8  | 5.5  | mA    |  |

| V <sub>DD</sub> Zener Clamp Current              | V <sub>CLAMP</sub>    | I <sub>VDD</sub> =20mA                     | 29   | 31   | 33   | V     |  |

| Under-Voltage Lockout Section                    |                       |                                            |      |      |      |       |  |

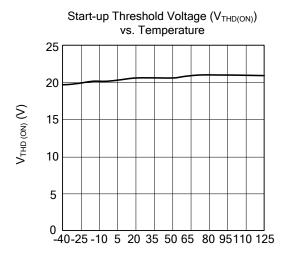

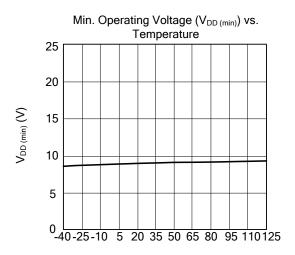

| Start Threshold Voltage                          | V <sub>THD (ON)</sub> |                                            | 18   | 20   | 22   | V     |  |

| Min. Operating Voltage                           | V <sub>CC (MIN)</sub> |                                            | 6.5  | 8    | 9.5  | V     |  |

| Control Section                                  |                       |                                            |      |      |      |       |  |

| Feedback Source Current                          | I <sub>FB</sub>       | V <sub>FB</sub> =0                         |      | 240  |      | uA    |  |

| V <sub>FB</sub> Open Loop Voltage Level          | V <sub>FB</sub> _Open |                                            |      | 5.4  |      | V     |  |

| Burst-Mode Out FB Voltage                        | V <sub>FB (OUT)</sub> | V <sub>CS</sub> =0                         |      | 1.42 |      | V     |  |

| Burst-Mode Enter FB Voltage                      | V <sub>FB (IN)</sub>  | V <sub>CS</sub> =0                         |      | 1.35 |      | V     |  |

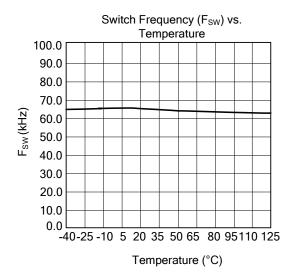

| Normal initial                                   |                       | V <sub>FB</sub> =3.5V                      | 60   | 65   | 70   | kHz   |  |

| Switching Frequency  Burst mode Base Frequency   | F <sub>(SW)</sub>     |                                            | 20   |      |      | kHz   |  |

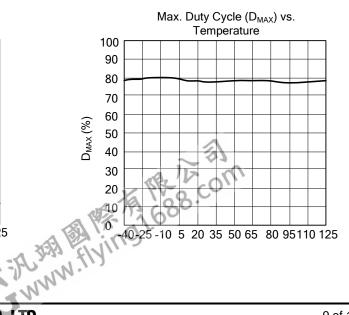

| Duty Cycle                                       | D <sub>MAX</sub>      | V <sub>FB</sub> =3.5V, V <sub>CS</sub> =0  | 70   | 80   | 90   | %     |  |

| Frequency Hopping                                | F <sub>J (SW)</sub>   |                                            | -9   |      | +9   | %     |  |

| Frequency Variation VS V <sub>CC</sub> Deviation | F <sub>DV</sub>       | V <sub>CC</sub> =10~20V                    |      |      | 10   | %     |  |

| Frequency Variation VS Temperature Deviation     | F <sub>DT</sub>       | T=-40~110°C                                |      |      | 10   | %     |  |

| Soft-Start Time                                  | T <sub>SOFTS</sub>    |                                            |      | 5    |      | ms    |  |

| Protection Section                               |                       |                                            |      |      |      |       |  |

| OVP threshold                                    | V <sub>OVP</sub>      | V <sub>FB</sub> =3.5V                      | 25   | 27   | 29   | V     |  |

| OLP Threshold                                    | V <sub>FB (OLP)</sub> | V <sub>CS</sub> =0                         |      | 4.4  |      | V     |  |

| Delay Time Of OLP                                | $T_{D-OLP}$           |                                            | 60   | 88   | 120  | ms    |  |

| OTP Threshold                                    | T (THR)               |                                            |      | 150  |      | °C    |  |

| Current Limiting Section                         |                       |                                            |      |      | ,    |       |  |

| Leading Edge Blanking Time                       | t <sub>LEB</sub>      |                                            | 200  | 450  | 700  | nS    |  |

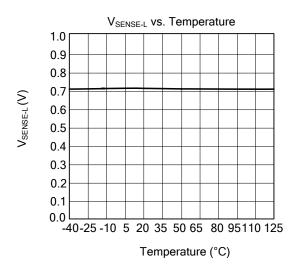

| Peak Current Limitation                          | V <sub>SENSE_H</sub>  | V <sub>FB</sub> =3.9V                      | 7    | 0.92 |      | V     |  |

| Threshold Voltage For Valley                     | V <sub>SENSE_L</sub>  | V <sub>FB</sub> =3.9V                      | 0.73 | 0.79 | 0.85 | V     |  |

| Power Mos-Transistor Section                     |                       |                                            |      |      |      |       |  |

| Drain-Source Breakdown Voltage                   | V <sub>DSS</sub>      | $V_{GS}$ =0V, $I_D$ =250 $\mu$ A           | 650  |      |      | V     |  |

| Turn-on Voltage Between Gate And Source          | V <sub>TH</sub>       | $V_{DS}=V_{GS}$ , $I_{D}=250\mu A$         | 2    |      | 4    | V     |  |

| Drain-Source Diode Continuous Source Current     | Js V                  | 3 109                                      |      |      | 8.0  | Α     |  |

| Static Drain-Source On-State Resistance          | RDS (ON)              | V <sub>GS</sub> =10V, I <sub>D</sub> =0.8A |      |      | 0.6  | Ω     |  |

Notes: 1. Pulse Test : Pulse width ≤ 300µs, Duty cycle ≤ 2%.

<sup>2.</sup> Essentially independent of operating ambient temperature.

#### **■ FUNCTIONAL DESCRIPTION**

The internal reference voltages and bias circuit work at V<sub>CC</sub>>V<sub>THD (ON)</sub>, and shutdown at V<sub>CC</sub><V<sub>CC (MIN)</sub>.

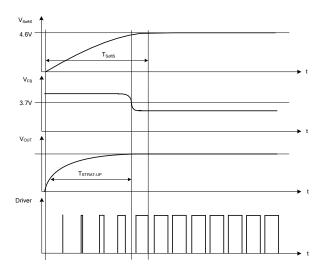

### (1) Soft-Start

When every IC power on, driver output duty cycle will be decided by inter-slope voltage  $V_{SOFTS}$  and  $V_{CS}$  on current sense resistor at beginning. After the whole soft-start phase end, and driver duty cycle depend on  $V_{FB}$  and  $V_{CS}$ . The relation among  $V_{SOFTS}$ ,  $V_{FB}$  and  $V_{OUT}$  as followed Fig.3. Furthermore, soft-start phase should end before  $V_{CC}$  reach  $V_{CC}$  (MIN) during  $V_{CC}$  power on. Otherwise, if soft-start phase remain not end before  $V_{CC}$  reach  $V_{CC}$  (MIN) during  $V_{CC}$  power on, IC will enter auto-restart phase and not set up  $V_{OUT}$ .

Fig.3 Soft-Start Phase

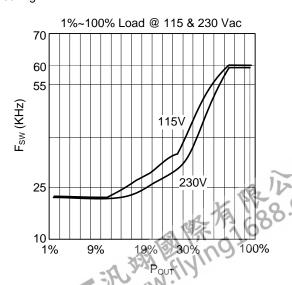

# (2) Switching Frequency Set

The maximum switching frequency is set to 65kHz. Switching frequency is modulated by output power  $P_{OUT}$  during IC operating. At no load or light load condition, most of the power dissipation in a switching mode power supply is from switching loss on the MOSFET transistor, the core loss of the transformer and the loss on the snubber circuit. The magnitude of power loss is in proportion to the number of switching events within a fixed period of time. So lower Switching frequency at lower load, which more and more improve IC's efficiency at light load. At from no load to light load condition, The IC will operate at from Burst mode to Reducing Frequency Mode. The relation curve between  $f_{SW}$  and  $P_{OUT}$  as followed Fig.4.

Fig.4 The Relation Curve Between Fsw And Relative Output Power Pout

# **FUNCTIONAL DESCRIPTION (Cont.)**

#### (3) Internal Synchronized Slope Compensation

Built-in slope compensation circuit adds voltage ramp onto the current sense input voltage for PWM generation, this greatly improves the close loop stability at CCM and prevents the sub-harmonic oscillation and thus reduces the output ripple voltage.

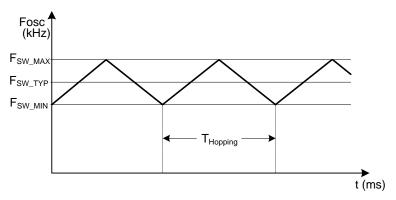

#### (4) Frequency Hopping For EMI Improvement

The Frequency Hopping is implemented in the IC; there are two oscillators built-in the IC. The first oscillator is to set the normal switching frequency; the switching frequency is modulated with a period signal generated by the 2nd oscillator. The relation between the first oscillator and the 2nd oscillator as followed Fig.5. So the tone energy is evenly spread out, the spread spectrum minimizes the conduction band EMI and therefore eases the system design in meeting stringent EMI requirement.

Fig.5 Frequency Hopping

# (5) Constant Output Power Limit

When the primary current, across the primary wind of transfer, reaches the limit current, the output GATE drive will be turned off after a small propagation delay t<sub>D</sub>. This propagation delay will introduce an additional current proportional to t<sub>D</sub>xV<sub>IN</sub>/Lp. Since the propagation delay is nearly constant regardless of the input line voltage V<sub>IN</sub>. Higher input line voltage will result in a larger additional current and hence the output power limit is also higher than that under low input line voltage. To compensate for this output power limit variation across a wide AC input range, the threshold voltage is adjusted by adding a positive ramp. This ramp signal rises from V<sub>SENSE\_L</sub> to V<sub>SENSE\_L</sub>, and then flattens out at V<sub>SENSE\_H</sub>. A smaller threshold voltage forces the output GATE drive to terminate earlier. This reduces the total PWM turn-on time and makes the output power equal to that of low line input. This proprietary internal compensation ensures a constant output power limit for a wide AC input voltage range (90VAC~264VAC).

# (6) Protection section

The IC takes on more protection functions such as OLP, OVP and OTP etc. In case of those failure modes for continual blanking time, the driver is shut down. At the same time, IC enters auto-restart, Vcc power on and driver is reset after V<sub>CC</sub> power on again.

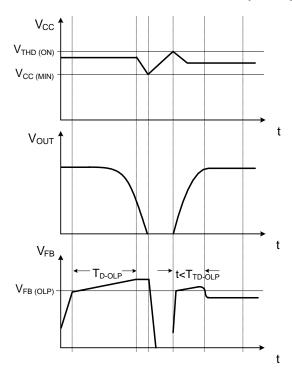

# **OLP**

After power on, IC will shutdown driver if over load state occurs for continual TD-OLP. OLP case as followed Fig.6.

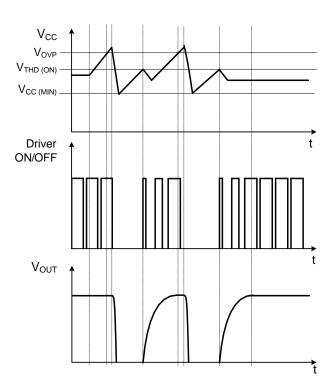

REFERENCE TO THE PROPERTY OF LIP OVP will shutdown the switching of the power MOSFET whenever V<sub>CC</sub>>V<sub>OVP</sub>. The OVR case as followed Fig.7.

# **■ FUNCTIONAL DESCRIPTION (Cont.)**

Fig.6 OLP Case

Fig.7 OVP Case

#### OTP

OTP will shut down driver when junction temperature  $T_J > T_{(THR)}$  for continual a blanking time.

### (7) Driver Output Section

The driver-stage drives the gate of the MOSFET and is optimized to minimize EMI and to provide high circuit efficiency. This is done by reducing the switch on slope when reaching the MOSFET threshold. This is achieved by a slope control of the rising edge at the driver's output. The output driver is clamped by an internal 15V Zener diode in order to protect power MOSFET transistors against undesirable gate over voltage.

The In addition to the gate drive control scheme mentioned, the gate drive strength can also be adjusted externally by a resistor connected between  $V_{DD}$  and  $V_{DDG}$ , the falling edge of the Drain output can be well controlled. It provides great flexibility for system EMI design.

#### (8) Inside power switch MOS transistor

Specific power MOS transistor parameter is as "POWER MOS TRANSISTOR SECTION" in electrical characteristics table.

# (9) FB pin

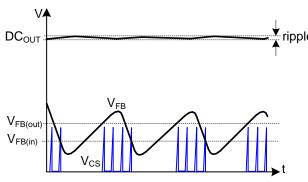

Greenmode and Burstmode is controlled by  $V_{FB}$ . Capacitor  $C_{FB}$  is connected between FB and GND.  $V_{FB}$  control switch frequency Fsw in greenmode.

C<sub>FB</sub>=0.33~2.2nF

in full load, V<sub>FB</sub> > 2.6V, have Fsw=65kHz.

In green mode,

$2V \le V_{FB} \le 2.6V$ , have Fsw= $72*V_{FB}$ -122 (kHz).

$V_{FB in} \leq V_{FB} \leq 2V$ , have Fsw=22 (kHz).

In burst mode, IC shutdown when  $V_{FB < V_{FB (in)}}$ , then DC output fall and  $V_{FB}$  rise, IC on/off work when

$V_{FB}$ > $V_{FB \ (out)}$ , then DC output rise and  $V_{FB}$  fall , IC shutdown when VFB<VFB (in) again. In burstmode, on/off times is related with Lp  $\$ fsw  $\$ Rcs etc. And unrelated with controller IC.

# **■ FUNCTIONAL DESCRIPTION (Cont.)**

Fig.8 DC Output,  $V_{FB}$ ,  $V_{CS}$  Timing

# (10) CS pin

Current sense input pin. Connected to MOSFET current sensing resistor node.  $R_{CS}$  is Current sense resistor.  $V_{cspk} = I_{pk} \times R_{CS} = (V_{FB} - V_{be}) / 3$ ,

In DCM mode,

$Lp = (V_{dc\_min} \textbf{x} D_{max}) \ \textbf{x} \ (V_{dc\_min} \textbf{x} D_{max}) \ / \ (2P_{in} \textbf{x} F_{sw})$

Lp is primary inductance,  $V_{dc\_min}$  is minimum DC voltage input, Dmax is maximum duty cycle, Pin is input power,  $F_{sw}$  is switch frequency.

In CCM mode,

$L_{\text{P=}} \ (V_{\text{dc\_min}} \textbf{x} D_{\text{max}}) \ \textbf{x} \ (V_{\text{dc\_min}} \textbf{x} D_{\text{max}}) \ / \ (2P_{\text{in}} \textbf{x} F_{\text{sw}} \textbf{x} K_{\text{RF}})$

K<sub>RF</sub>=0.3~0.5 is input voltage ripple coefficient, usually K<sub>RF</sub>=0.5.

$$Pin = \frac{1}{2} * Lp * Fsw * lpk^2$$

So, we can Calculate  $I_{PK}$  and  $R_{CS}$ .

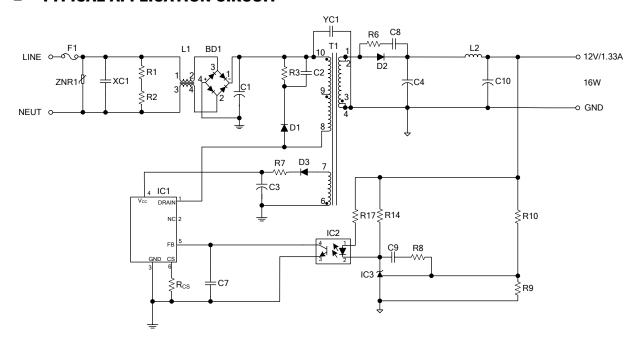

# TYPICAL APPLICATION CIRCUIT

Fig.9 UTC UCS1657S Typical Application Circuit

UNISONIC TECHNOLOGIES CO., LTD

www.unisonic.com.tw

# **■ TYPICAL CHARACTERISTICS**

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.