圖片僅供參考

74HC573D,653 SOIC-20 NXP

| 附件下載 | |

| 商品名稱 | Octal D-type transparent latch; 3-state |

| 訂購數量 | |

| 依數量訂價 | 20 NTD |

| FLYiNG 零件編號 | IC74HC573D653NEXPERIA |

| FLYiNG 散料庫存 | 265 |

| FLYiNG 標準包裝庫存 | 2,000 |

| 製造商/品牌商 | NEXPERIA |

| 製造商/品牌商零件編號 | 74HC573D,653 |

| 說明 | 74HC573D,653 SOIC-20 NXP |

| 無鉛狀態 / RoHS 指令狀態 | RoHS |

| 散裝數量 | NTD 單價 / PCS |

| 1~9 | 20 |

| 10~99 | 18 |

| 100~2499 | 16 |

| 2500~ | 12 |

| 積體電路類型 | CMOS IC |

| 電路數 | 8 Circuit |

| 極性 | Non-Inverting |

| 靜止電流 | 8 uA |

| 輸出行數 | 8 Line |

| 高電平輸出電流 | - 7.8 mA |

| 傳播延遲時間 | 14 ns at 5 V |

| 電源電壓 | 2~6 V |

| 工作溫度 | -40~125°C |

| 封裝/外殼 | SOIC-20 |

| 安裝類型 | SMD 表面黏著式 |

| 標準包裝數量 | 2000/REEL |

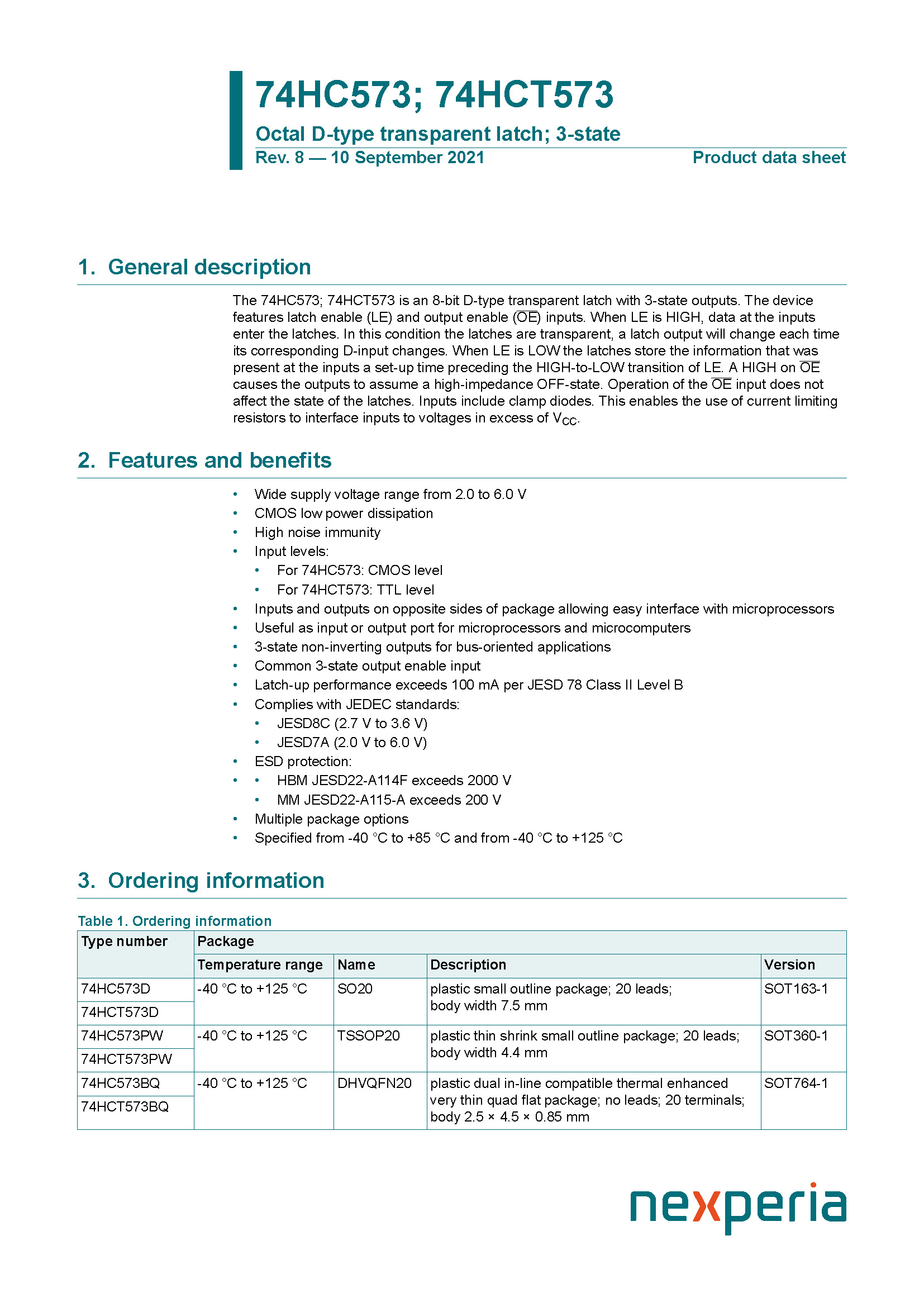

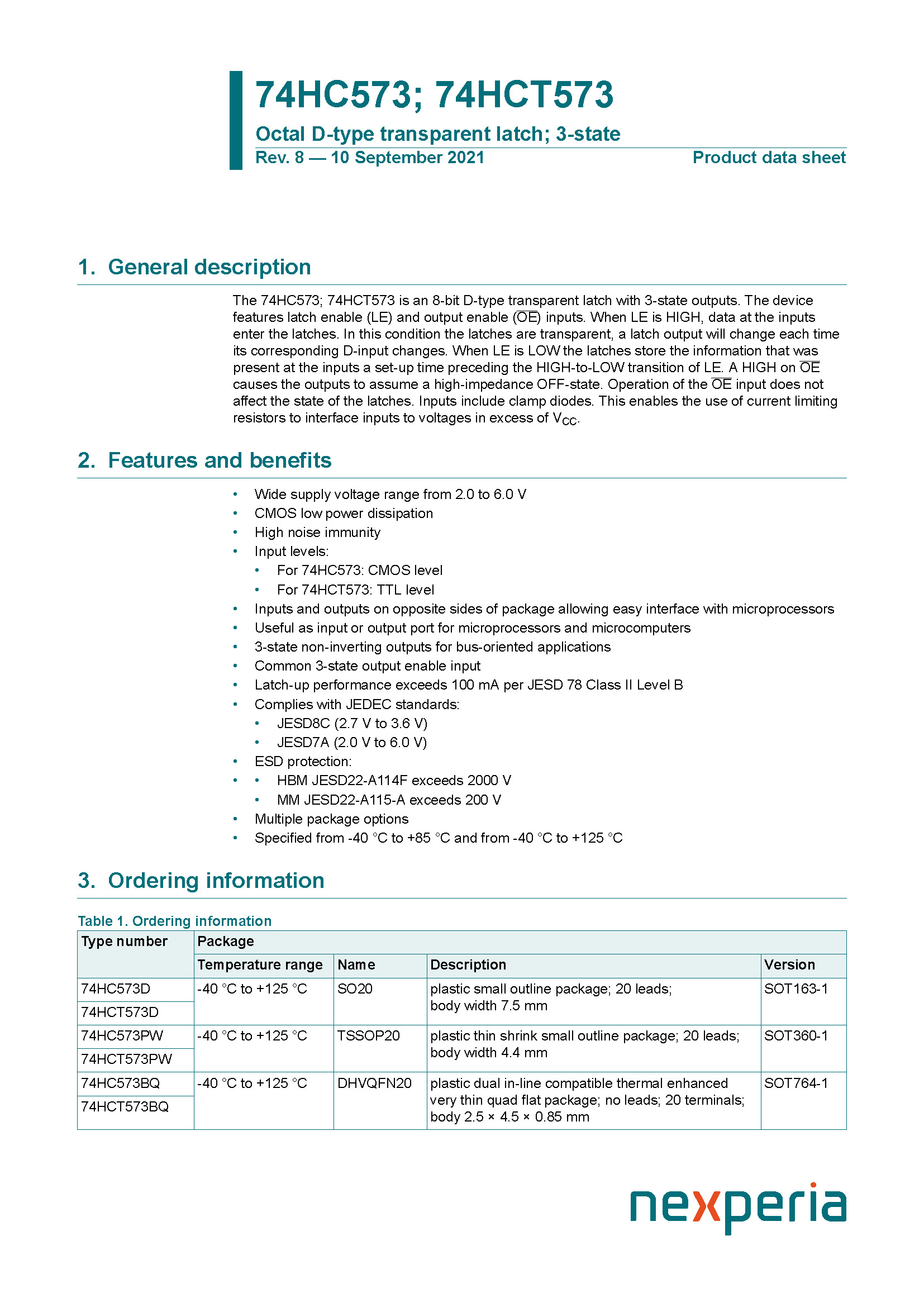

74HC573; 74HCT573

Octal D-type transparent latch; 3-state

General description

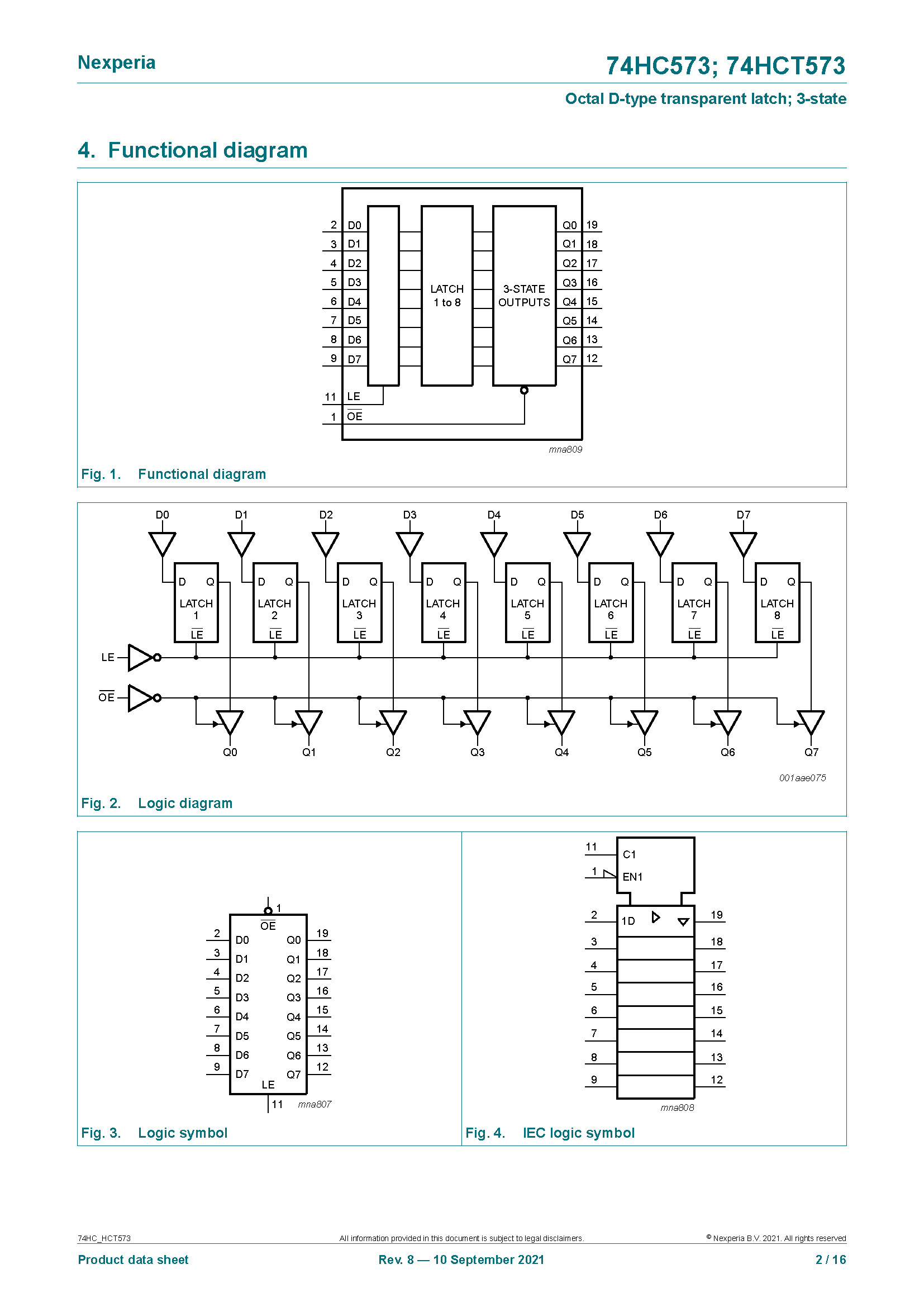

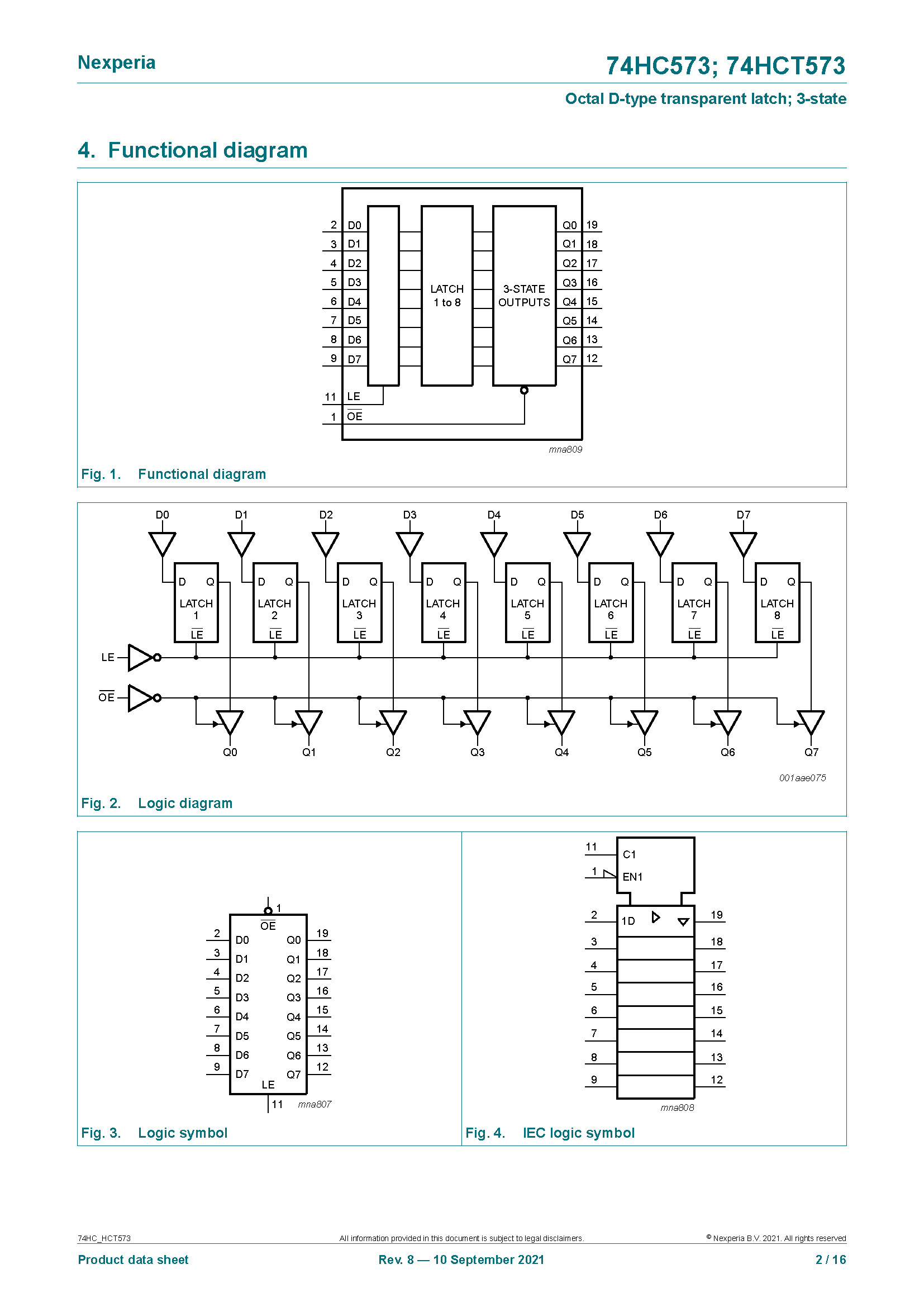

The 74HC573; 74HCT573 is an 8-bit D-type transparent latch with 3-state outputs. The device features latch enable (LE) and output enable (OE) inputs. When LE is HIGH, data at the inputs enter the latches. In this condition the latches are transparent, a latch output will change each time its corresponding D-input changes. When LE is LOW the latches store the information that was present at the inputs a set-up time preceding the HIGH-to-LOW transition of LE. A HIGH on OE causes the outputs to assume a high-impedance OFF-state. Operation of the OE input does not affect the state of the latches. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

Features and benefits

74HC573; 74HCT573

八路D型透明鎖存器;三態

一般說明

74HC573; 74HCT573 是一個具有三態輸出的 8 位 D 型透明鎖存器。該器件具有鎖存使能 (LE) 和輸出使能 (OE) 輸入。當 LE 為高電平時,輸入端的數據進入鎖存器。在這種情況下,鎖存器是透明的,每次對應的 D 輸入發生變化時,鎖存器的輸出都會發生變化。當 LE 為低電平時,鎖存器存儲在 LE 的高電平到低電平轉換之前的設置時間出現在輸入端的信息。 OE 上的高電平導致輸出呈現高阻抗關斷狀態。 OE 輸入的操作不會影響鎖存器的狀態。輸入包括箝位二極管。這使得可以使用限流電阻將輸入連接到超過 VCC 的電壓。

特點和好處

Octal D-type transparent latch; 3-state

General description

The 74HC573; 74HCT573 is an 8-bit D-type transparent latch with 3-state outputs. The device features latch enable (LE) and output enable (OE) inputs. When LE is HIGH, data at the inputs enter the latches. In this condition the latches are transparent, a latch output will change each time its corresponding D-input changes. When LE is LOW the latches store the information that was present at the inputs a set-up time preceding the HIGH-to-LOW transition of LE. A HIGH on OE causes the outputs to assume a high-impedance OFF-state. Operation of the OE input does not affect the state of the latches. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

- Wide supply voltage range from 2.0 to 6.0 V

- CMOS low power dissipation

- High noise immunity

- Input levels:

- For 74HC573: CMOS level

- For 74HCT573: TTL level

- Inputs and outputs on opposite sides of package allowing easy interface with microprocessors

- Useful as input or output port for microprocessors and microcomputers

- 3-state non-inverting outputs for bus-oriented applications

- Common 3-state output enable input

- Latch-up performance exceeds 100 mA per JESD 78 Class II Level B

- Complies with JEDEC standards:

- JESD8C (2.7 V to 3.6 V)

- JESD7A (2.0 V to 6.0 V)

- ESD protection:

- HBM JESD22-A114F exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- Multiple package options

- Specified from -40 °C to +85 °C and from -40 °C to +125 °C

74HC573; 74HCT573

八路D型透明鎖存器;三態

一般說明

74HC573; 74HCT573 是一個具有三態輸出的 8 位 D 型透明鎖存器。該器件具有鎖存使能 (LE) 和輸出使能 (OE) 輸入。當 LE 為高電平時,輸入端的數據進入鎖存器。在這種情況下,鎖存器是透明的,每次對應的 D 輸入發生變化時,鎖存器的輸出都會發生變化。當 LE 為低電平時,鎖存器存儲在 LE 的高電平到低電平轉換之前的設置時間出現在輸入端的信息。 OE 上的高電平導致輸出呈現高阻抗關斷狀態。 OE 輸入的操作不會影響鎖存器的狀態。輸入包括箝位二極管。這使得可以使用限流電阻將輸入連接到超過 VCC 的電壓。

特點和好處

- 2.0 至 6.0 V 的寬電源電壓範圍

- CMOS低功耗

- 高抗噪性

- 輸入電平:

- 對於 74HC573:CMOS 電平

- 對於 74HCT573:TTL 電平

- 封裝兩側的輸入和輸出允許與微處理器輕鬆連接

- 可用作微處理器和微型計算機的輸入或輸出端口

- 面向總線應用的三態非反相輸出

- 通用三態輸出使能輸入

- 閂鎖性能超過 100 mA,符合 JESD 78 Class II Level B

- 符合 JEDEC 標準:

- JESD8C(2.7V 至 3.6V)

- JESD7A(2.0 V 至 6.0 V)

- ESD保護:

- HBM JESD22-A114F 超過 2000 V

- MM JESD22-A115-A 超過 200 V

- 多種包裝選擇

- 指定範圍為 -40 °C 至 +85 °C 和 -40 °C 至 +125 °C